Part Number: MSPM0G3507

Other Parts Discussed in Thread: SYSCONFIG

Hi,

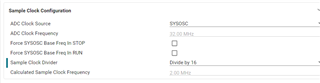

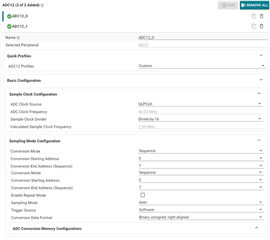

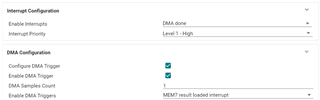

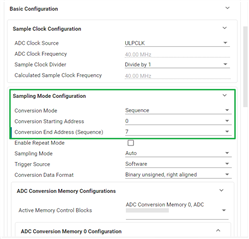

In my application I am using all 16 channels of the 2 ADC modules, in sequence conversion mode and auto sampling mode. What is the maximum Calculated Sample Clock Frequency that can be set? Doing a bit of testing I can't get above 2.5MHz, UPCLK(40MHz) with 16 of Sample Clock divider. Is it possible to increase the frequency further?

Regards