Other Parts Discussed in Thread: TM4C1294NCPDT

Hello,

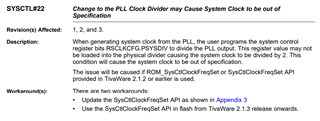

We are facing an issue with the pll clock and the fvco within the TM4C129NCPDT.

We cannot run at vco 480 Mhz and Pll / Sysclk at 120 Mhz which are the max as shown in the table of TM4C1294NCPDT__DS__2014-06-18__SPMS433B.

TM4C1294NCPDT__DS__2014-06-18__SPMS433B is from 2014 are there some newer datasheets? The Sysclk will not run faster than 25 Mhz.

We are using the Tiva C Series TM4C129 Connected Launchpad evaluation kit.

This video shows also different values and equation to calculate the pll and sysclk https://www.ti.com/video/3881419229001#tab-1

Which equation is now correct? Can you tell me? We are not using any TI lib or code, so we need to know how it works.

Thank you.