Other Parts Discussed in Thread: SYSCONFIG

Hi,

1. In TRM under section 13.5.1.1.1 RTI Features, it is mentioned as

"Two independent 64 bit counter blocks (counter block0 or counter block1). Each block consists of

- One 32 bit up counter

- One 32 bit free running counter"

Is it possible to combine both counter and use as single 64bit counter.

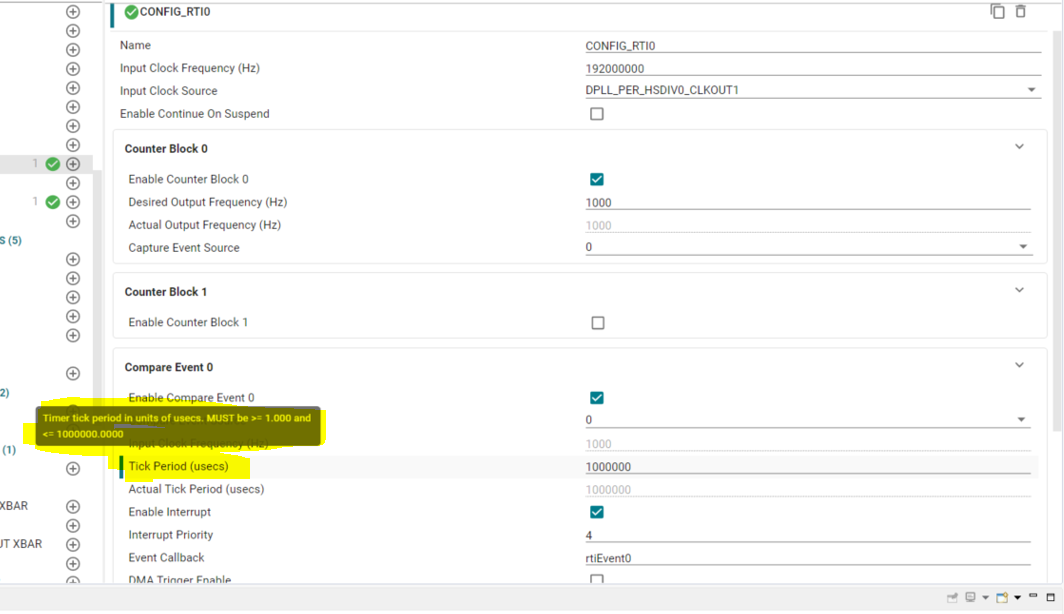

2. In the CCS, under RTI configuration section for "Tick Period (usecs)" it is mentioned as "Timer tick period in units of usecs. Must be greater than equal to 1 and less than equal to 1000000"

I'm interested in finding, what is the maximum time interval I can able to generate interrupt using RTI, by configuring the compare block to generate event at particular period.

For example if I'm configuring 32bit timer with 1MHz and timer counter will increment for each 1us(1/1MHz). So maximum possible time interval, to generate an event is [1us * (2^32)] => [1us * 4,294,967,295] => 4,294.96 secs, for this I need to configure the Period to 4,294,967,295 but in the CCS Tick Period (usecs) showing in the unit of usecs and maximum value showing is 1000000us (which is one sec).

So the maximum possible event generation is one sec only Or What if I need to configure the event generation for every 100sec or maximum possible ?