Other Parts Discussed in Thread: TPS735, TPS717

Hello forum gurus,

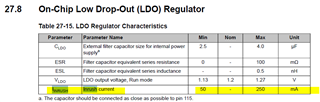

Why the datasheet current consumption table and LDO table 27-63 does not show a formula (Iinrush) though table 27-8 shows LDO ranges 50mA - 150mA? Do we assume LDO Iirush depends on how many peripherals are enabled after POR? It's not a launch pad sporting 500mA LDO though seem to recall runtime current being roughly 78mA steady state. Was there ever Tina model made for TM4C1294?

Table shows all peripherals off (65.3mA 105°C) so we have to also add LDO inrush to that? Also does not account for 3v3 rail capacitors and any bulk caps in the circuit though large capacitance on 3v3 rail slows down the rate of total inrush via external LDO.

So external 500mA -1A LDO regulator is no big mystery but downsizing to external 150mA LDO raises some questions. For instance, C2000 MCU current consumption might reach >170mA during flash write. I could not find any similar datasheet text TM4C flash write via internal LDO or external 3v3 rail though seem to recall it being mentioned this forum some time ago.

The trade off on external LDO current seems to be relative to PSRR range to that of high frequency buck regulators that may supply LDO input.