Other Parts Discussed in Thread: AM2732

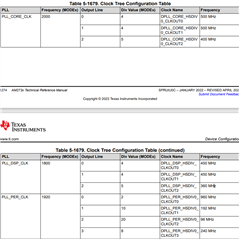

Can AM2732 output clock frequencies of 150MHz or 200MHz?

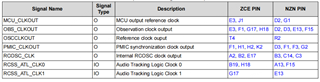

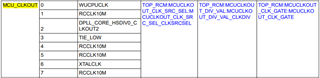

I need AM2732 to provide a reference clock for a high-speed parallel interface of an external device. I noticed that AM2732 does have some clock output pins. What is the frequency range of these clock outputs?