Other Parts Discussed in Thread: SYSCONFIG

Hi,

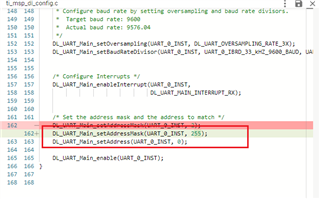

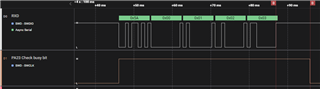

I would like to use the UART in IDLE line mode, but I cannot get the result indicated by the datasheet, the busy signal does not remain set while receiving data.

I tested several different configurations, on UART0 and UART1 in extend or main mode, I always have the same behavior.

Would it be possible to have a working example configuration ?