■SORTE_G, デバイスからアプリケーションに割り込みイベントがあがらない

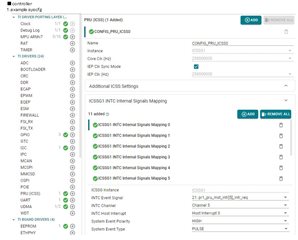

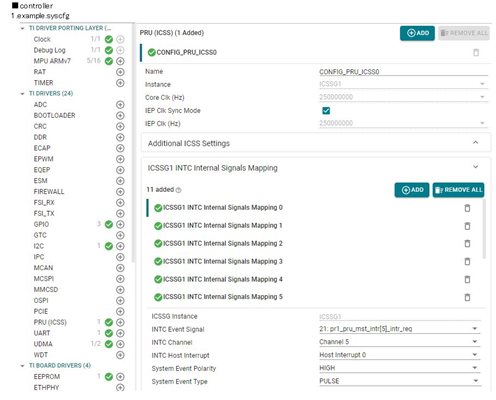

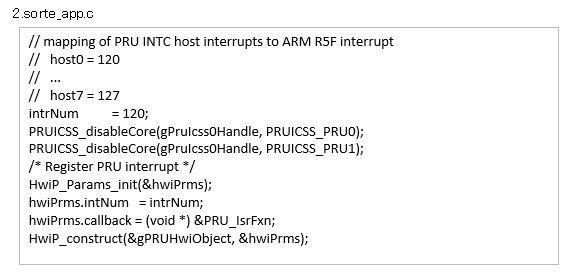

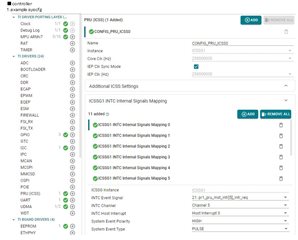

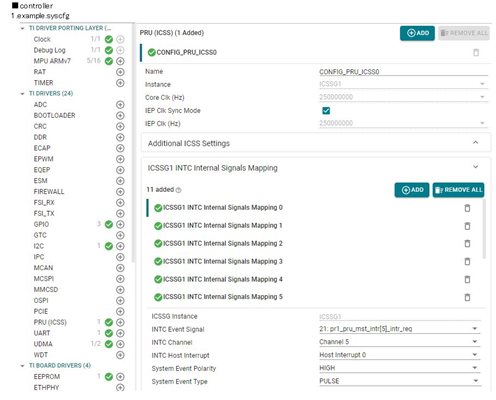

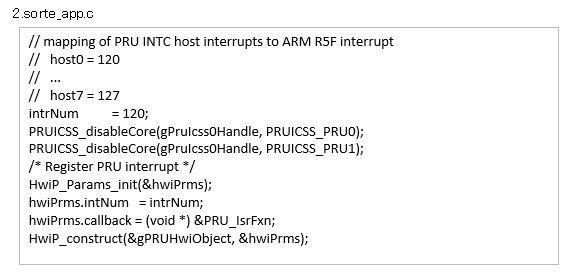

デバイスで設定した割り込みイベントがアプリケーションで受信できません。

不足している設定はありますでしょうか?

■SORTE_G, interrupt event does not occur from device to application

The application cannot receive the interrupt event set on the device.

Are there any settings that are missing?