Other Parts Discussed in Thread: SYSCONFIG, UNIFLASH

Hello,

I have tried to use two enet examples from mcu_plus_sdk_am263px_09_01_00_20 but neither are able to get an IP address via DHCP. For example: enet_lwip_cpsw_am263px-cc_r5fss0-0_freertos_ti-arm-clang

The Terminal output is:

==========================

ENET LWIP App

==========================

EnetAppUtils_reduceCoreMacAllocation: Reduced Mac Address Allocation for CoreId:0 From 4 To 2

Link Status Changed. PHY: 0x0, state: up

EnetPhy_bindDriver:1828

PHY 0 is alive

Starting lwIP, local interface IP is dhcp-enabled

[LWIPIF_LWIP] NETIF INIT SUCCESS

Host MAC address-0 : 70:ff:76:1f:60:20

[LWIPIF_LWIP] Enet has been started successfully

[0]status_callback==UP, local interface IP is 0.0.0.0

UDP server listening on port 5001

Cpsw_handleLinkUp:1629

MAC Port 2: link up

link_callback==UP

5. 44s : CPU load = 1.17 %

10. 44s : CPU load = 0.98 %

IP address is always 0.

I am using the same cable that was plugged into my oscilloscope where I could access its http server. So cabling and router DHCP are working fine.

The RJ45 LEDs indicate as follows:

Left hand (closest to USB-C) : steady yellow.

Right hand : intermittent green.

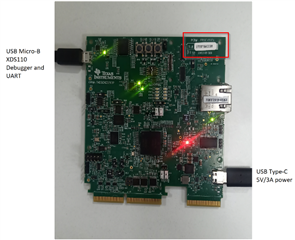

Please can you confirm if any of the examples are running correctly out of the box on TMDSCNCD263P.

Thank you.