Other Parts Discussed in Thread: TMS570LS3137, HALCOGEN

Hi there,

I have 2 different project working on TMS570LC4357 MCU.

On my first project, I'm using freeRTOS and cache is enabled (write-through) for flash memory. On the second project, I don't use freeRTOS, but the cache settings are the same.

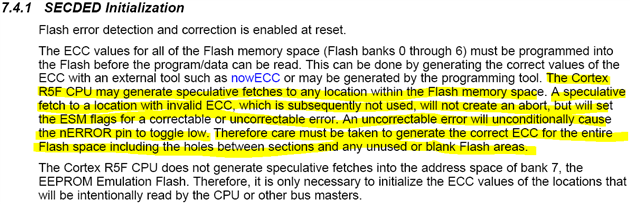

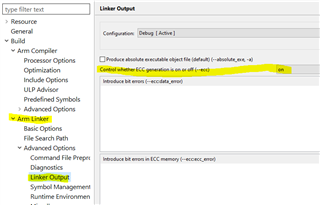

On my first project I'm getting an error from ESM group 2 channel 3 even when cache is disabled. I think this error is getting because of speculative instruction fetch operation and in this case I know that 2 different solutions. But my second project doesn' recieve any esm error (actually when I do flash bank 7 write operation, esm error recieves). What could be the difference?

According to the ARM Cortexv7-R manual, the CPU uses speculative instruction fetch, but in this case this error should occur in both projects. Both projects are too large, so there must be an ecc error depending on the speculative instruction fetch operation.

Is there any known issue with using freertos specifically and why is it related to using flash bank 7 or fapi?