Other Parts Discussed in Thread: SYSCONFIG

Hello,

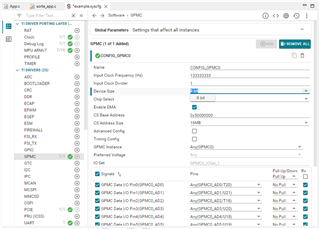

I have noticed that in the datasheet of AM243x it is mentioned that there is support for 16-bit memory in GPMC.

However when configuring the device in SysConfig, I am unable to select 16-bit and the only option is 8-bit.

See this picture below with SDK Version 9.1, CCS 12.3, SysConfig 18.0.

Thanks and regards

Manuel