Hi expert,

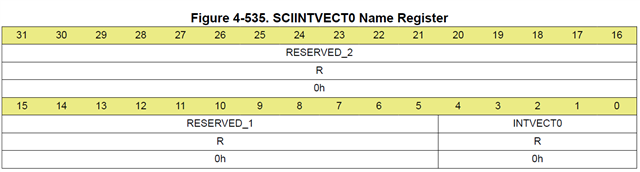

I have questions regarding LIN_SCIINTVECT register.

From register description:

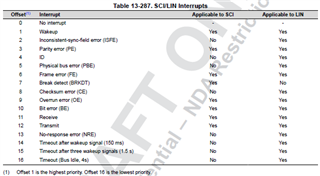

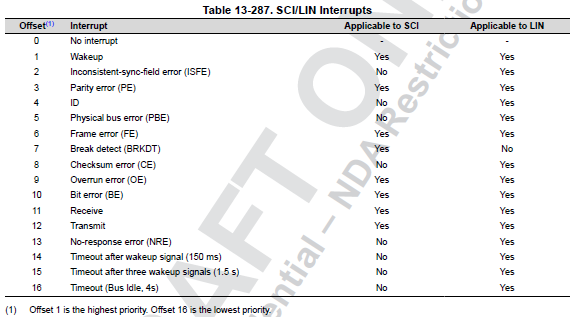

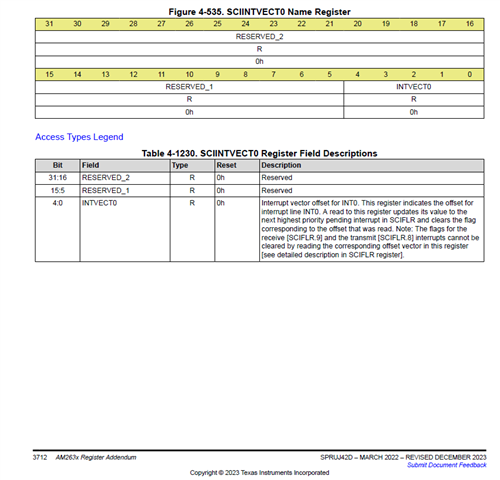

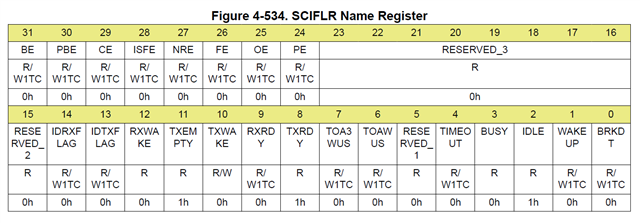

Interrupt vector offset for INT0. This register indicates the offset for

interrupt line INT0. A read to this register updates its value to the

next highest priority pending interrupt in SCIFLR and clears the flag

corresponding to the offset that was read.

But from the source code, I can't not see any relationship in between this vector value and SCIFLR

/** @} */

/**

* \anchor LIN_IntOffset

* \name Lin Interrupt Offset

*

* Note: Definitions for the return value of LIN_getInterruptLine0Offset()

* and LIN_getInterruptLine1Offset().

*

* @{

*/

#define LIN_VECT_NONE (0x00)

#define LIN_VECT_WAKEUP (0x01)

#define LIN_VECT_ISFE (0x02)

#define LIN_VECT_PE (0x03)

#define LIN_VECT_ID (0x04)

#define LIN_VECT_PBE (0x05)

#define LIN_VECT_FE (0x06)

#define LIN_VECT_BREAK (0x07)

#define LIN_VECT_CE (0x08)

#define LIN_VECT_OE (0x09)

#define LIN_VECT_BE (0x0A)

#define LIN_VECT_RX (0x0B)

#define LIN_VECT_TX (0x0C)

#define LIN_VECT_NRE (0x0D)

#define LIN_VECT_TOAWUS (0x0E)

#define LIN_VECT_TOA3WUS (0x0F)

#define LIN_VECT_TO (0x10)

/** @} */

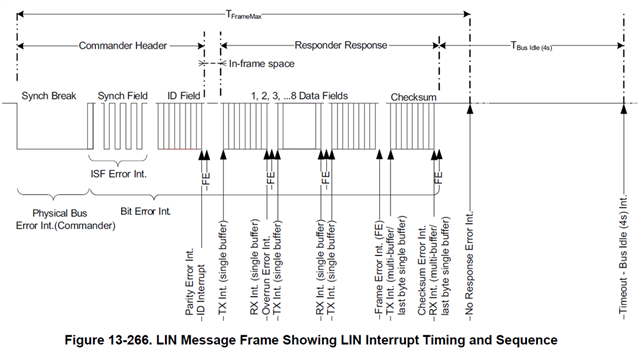

For example: when LIN in responder mode received ID, we got LIN_VECT_ID (0x04) from reading LIN_SCIINTVECT by -LIN_getInterruptLine0Offset () API.

However the FIDRXFLAG in SCIFLR is bit 14. The vector offset is not corresponding to vector offset. I'm confusing.

Any document to describe vector value in between each flag in SCIFLR and SCIINTVECT value?

After reading vector, only flags for the receive [SCIFLR.9] and the transmit [SCIFLR.8] interrupts need to be cleared manually. Is this correct?

Regards

Andre