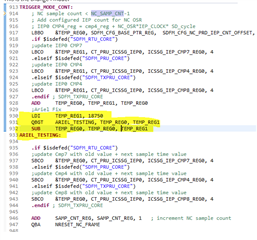

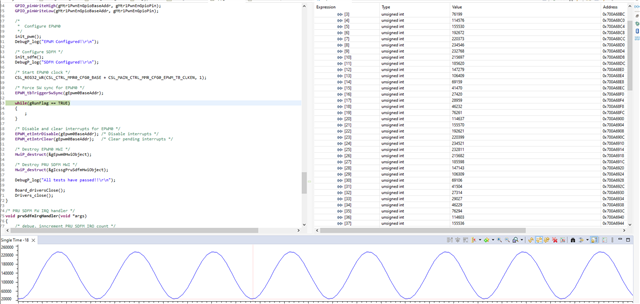

I've added the following code:

OSR is 64, normal current only.

16Khz

double sampling is on.

I'm having noisy samples every 26 or so samples.

Please advise

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

I've added the following code:

OSR is 64, normal current only.

16Khz

double sampling is on.

I'm having noisy samples every 26 or so samples.

Please advise

Hi Ariel,

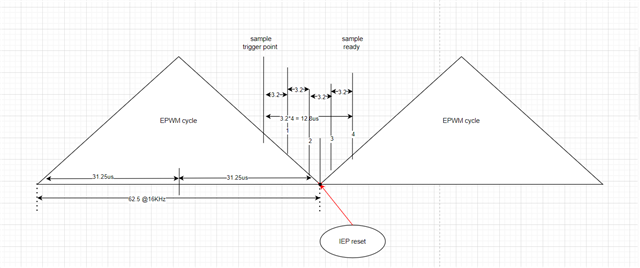

In our sdfm firmware we are resetting the IEP from the EPWM sync0 out event and the EPWM and ICSS clock are generated from different clock source, so EPWM sync0 out event is adding random jitter to the IEP rest. Due to this jitter, the SDFM firmware is reading data from the accumulator at 65 OSR instead of 64. This means that out of 3 consecutive samples we are reading some samples at 64 and some samples at 65. Due to these 64 and 65 combinations, the filter registers value is not coming in stable state for OSR 64 and giving incorrect data.

To avoid jitter, you can use any one of the suitable methods given below.

It would be great if you shared the list of features you want, that way I can provide some other solutions to avoid this jitter.

Please select the features you want to support!

BR,

Achala Ram

Hi Achala,

I have aligned with STX and commenting for them:

Thanks Eyal,

Zero cross comparator: It detects the zero-cross by toggling the GPIO pin when the sd sample crosses the zero-cross threshold.

please see zero cross comparator section: AM243x Motor Control SDK: SDFM Interface Design (ti.com)

Can you please clarify few more things:

Regards,

Achala Ram

Thanks maor,

Over current and fast detection are two different features for error detection, I am sharing details about them which will help you understand the difference between them.

Fast detect: Each sigma delta channel has a hardware block just for fast over current detection, this block comparatively measures the number of zeros and ones presented in a programmable sliding window of 4 to 32 bits. It starts the comparison after the first 32 sample clocks. Based on the configured zero max/min count limits, it compares zero counter with these limits. If zero counter crosses limit, then it sends an error signal to respective PWM Trip zone block. PWM TZ block receives this error signal and sets trip status bit to bring TZ_OUT pin output state to high.

This block does zero/one compression with the raw data, I mean whatever input we pass on the SD channel, it reads the data bit by bit and after first 32 bit it starts zero/one compression. So it has very low latency (1.6us @20Mhz SD clock) and is faster than OC.

see fast detect section here:AM243x Motor Control SDK: SDFM Interface Design (ti.com)

Over current: It has higher latency than the fast detect block because in over current after executing the SINC3 filter on the sd_in data, the firmware compares the SINC3 filter output with the high and low threshold limits. If the output value exceeds the limit, then the firmware sets the overcurrent error bit of the corresponding PWM trip zone block. The PWM TZ block receives this error signal and sets the trip status bit to bring the TZ_OUT pin output state to HIGH.

see over current section for more details: AM243x Motor Control SDK: SDFM Interface Design (ti.com)

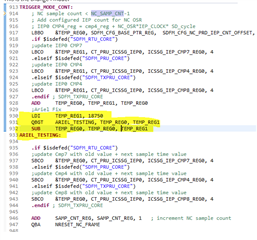

and also see this figure for sigma delta hardware:

Each SD channel only has one associated PWM TZ block, so if you use these features together, the detected error signal may collapse. So it would be better to use one feature!

Thanks & Regards,

Achala Ram

Hi maor,

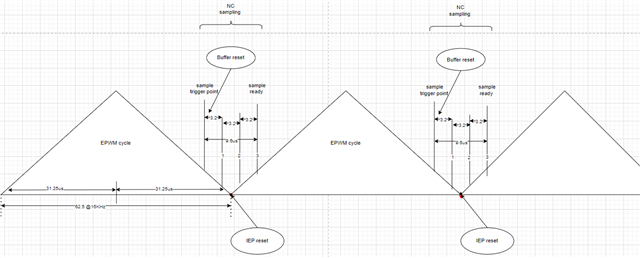

I saw that you need to clear the buffers after each interrupt in NC, but as we know the accumulator registers and flags are common for both NC and OC, so resetting the accumulator will cause problems in OC samples. Because the OC is free run, and we are resetting the accumulator registers and flags in between OC samples.

So can you clarify why you need to clear the buffers after each interrupt?? Because with buffers cleared you will not be able to use OC.

Hi Ram,

We need to clear the buffers before the first sample.

We have a very specific timings which we want to return the current measured value.

As I was saying, we are sampling 2 times in 16kHz.(enabling double update).

Since IEP reset clears the buffers for the first sample we have no issue here.

For the second sample, for our needs, we have to reset the buffers manually (for accurate values).

Hi Ariel,

Without clearing the buffers, the sample values will be accurate because we sample three times continuously for a correct NC sample, so what is inside the buffers before starting the NC sample does not affect the final result.

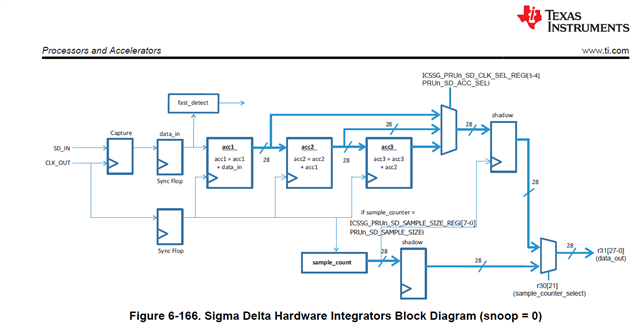

We did not observe any difference between sample values without clearing buffers and sample values with clearing buffers. I am sharing the sample values here where you can see that the sample data range is almost the same in both cases!

Clarification: IEP reset does not clear accumulator registers and flags, so you have to clear SD buffers manually even for the first sample!

Thanks & Regards,

Achala Ram

Hi Ram

Thanks for the clarification. In that case the fast detect is prefered.

Maor

Hi Maor,

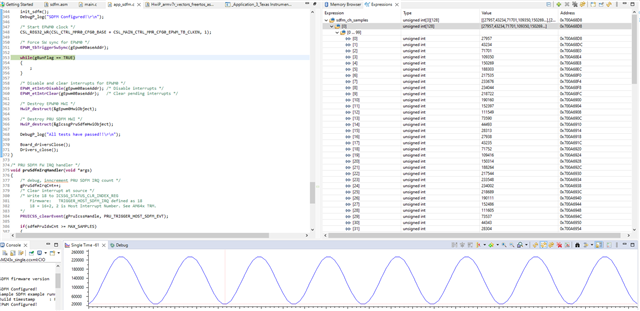

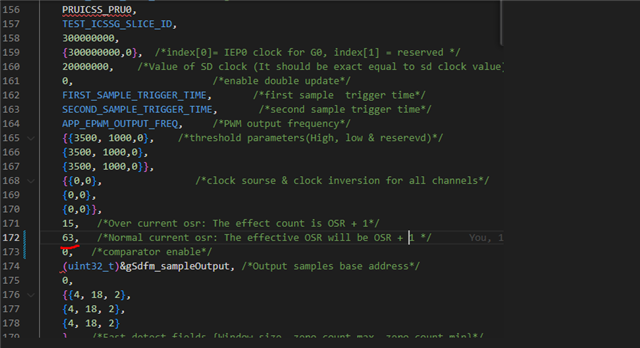

To avoid this jitter/noise, I am sharing some methods, you can use any one of them. (OSR64, SD clock 20 MHz)

Application-level changes: Since we are starting the Task 1 OSR early, so you have to pass the NC OSR value 63 instead of 64

Thanks & Regards,

Achala Ram