Part Number: MSP432E401Y

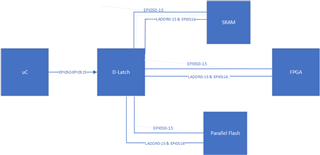

I'm currently designing a microcontroller board with MSP432E401Y which uses EPI Host bus muxed mode for interfacing with 3 devices(SRAM, Parallel Flash and FPGA)

To segregate the address and data line, should i add a D-latch for EPI( Referred https://www.ti.com/tool/TIDM-TM4CFLASHSRAM)

Or the internal ALE pin will capture the address and send accordingly?

Is it fine if i directly connect the EPI pins to the devices as A0-EPI0 and D0-EPI0 ?

Please let me know if there is anything that i have to add in my hardware design