Other Parts Discussed in Thread: SYSCONFIG

Hi TI Teams,

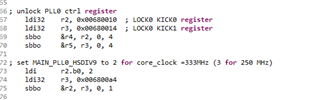

Situation: Run ethercat firmware under ICSSG1 in the r5f-0-0 core of am243, and run FSI firmware under ICSSG0 in the r5f-0-0 core. There is a code segment in ICSSG0 PRU as follows: .

.

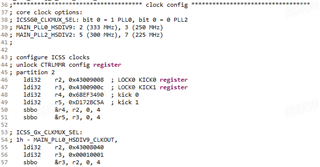

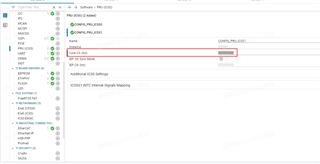

And with these code, the core clock of ICSSG1 running Ethercat can only be configured to 33333333Hz to run Ethercat normally as the following picture shows.

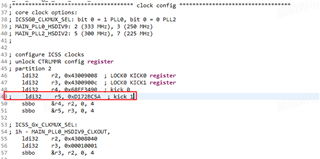

But if the code 'ldi32 r5, 0xD172BC5A ; Kick 1' in ICSSG0 firmware, as shown in the red box in the figure below, is masked. The core clock of ICSSG1 running Ethercat can be configured to run at other frequencies, such as 200000000Hz, and Ethercat can still run normally.

So why does this sentence in ICSSG0 affect the core clock configuration in ICSSG1? What role did this sentence 'ldi32 r5, 0xD172BC5A; kick 1 'play?

And I also want to know which clock source is the core clock of ICSSG1 running Ethercat firmware? Where was it configured?

Thanks.