Hello,

1. The current R5 main frequency is 400MHz, and it is stated in the manual that EPWM belongs to the ControlSS module. Should I configure ControlSS-PLL-CLK-SRC-SEL to select DPLL-CORE-HSDIV0-CLKOUT 2 (400MHz), and then the PWM division coefficient is 1? Is my PWM fundamental frequency 400MHz?

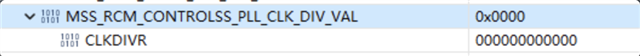

2. Import the demo project epwm_hr_duty_cycle-am263x-cc_r5fss0-0_2ortos_ti-arm lang, and the resulting PWM cycle is 1ms, 1Khz. Then, the division coefficient DIV is 4, and the uplink mode count is 25000. Therefore, I calculate that the input clock for PWM should be 200MHZ. During debugging, the ControlSS clock configuration is shown in the figure

From the register configuration, it can be seen that the ControlSS clock is at 400MHz. Why is it back calculated at 200MHz? Do I see that SYS-CLK is 200MHZ and the PWM input clock is SYS-CLK?

Regards,

Gary