Part Number: AM2434

Can Ethercat run on the M4 core? What modifications do I need to make?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi guxl24,

Thanks for your query.

Can Ethercat run on the M4 core?

Can you help me to understand the use case ? Why you want to move from R5F to M4 ?

One side effect I can see is PRU-ICSSG access latency will increase, which may not be acceptable for EtherCAT use case.

Best Regards

Ashwani

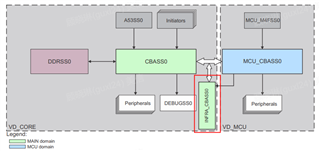

What I want to do is that ESC Firmware still runs on the R5 core’s PRU-ICSS, but the protocol stack runs on the M4 core. Since the protocol stack requires reading and writing ESC registers, is it possible for the M4 core to cross read and write ESC registers in the R5 core's PRU-ICSS through the INFRA-CBASS0 Interconnect shown in the figure below?

Thanks guxl24,

Please allow me some time to discuss this internally and get back to you.

Best Regards

Ashwani