Other Parts Discussed in Thread: AM3358

Hi,

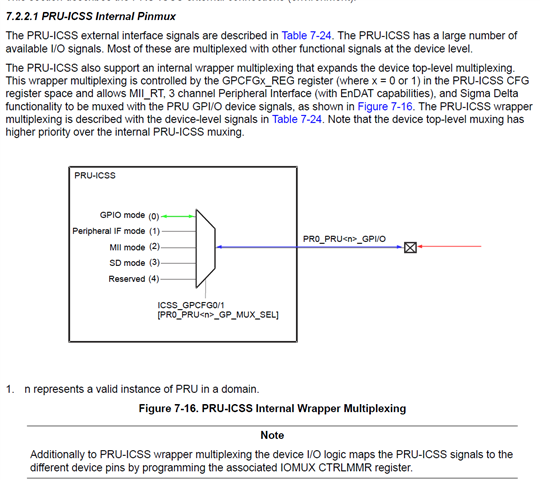

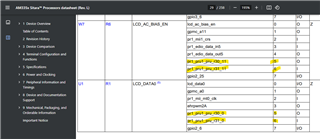

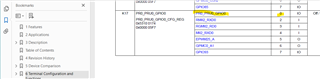

I have a question about routing the eGPI and eGPO to the device-level pins. According to the Datasheet, the PR0_PRUn_GPIO mode can be configured for a pin at a device level, however I couldn't find any information about configuring that pin to be an input (connected to eGPI and read from R31) or an output (connected to eGPO and modified through R30). For example, both eGPI0 and eGPO0 from PRU0 are muxed to PR0_PRU0_GPIO0 on Pin K17. What register contains the mux setting?

Thanks,

Pouya