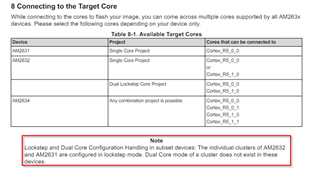

Part Number: AM2632

Hello,

we are using AM2632 and I have a question about the possiblities of bootflow.

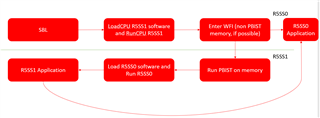

We use the AM2632 in lockstep mode, so we have two available cores (R5SS0 and R5SS1)

Is it possible to load firmware to R5SS1 from SBL and then start the firmware on R5SS1.

In the next step the R5SS1 should load firmware from flash to R5SS0 and start this on R5SS0.

Is this sequentiell load of firmware images possible(SBL loads to R5SS1 laods to R5SS0) ?

Background of my question is the execution of pBIST on R5SS1 (which tests R5SS0 memory areas), before loading firmware to R5SS0.

Best regards

Jo Scho