Other Parts Discussed in Thread: PROFIBUS

Hi TI experts,

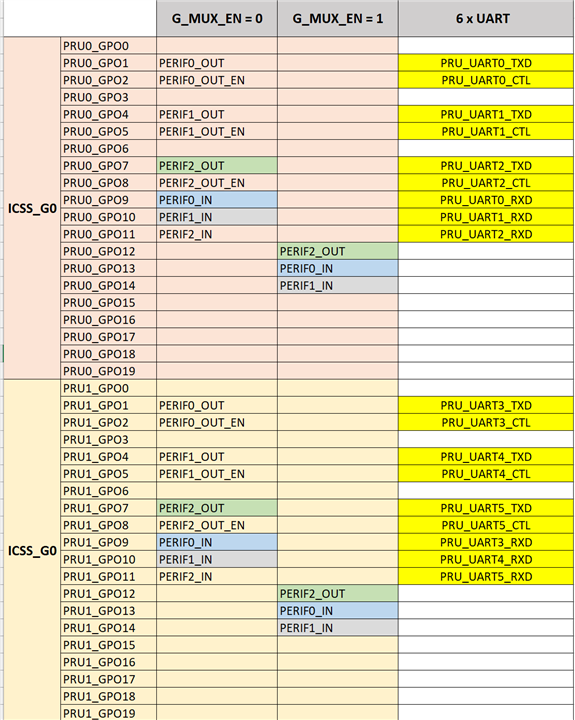

The AM243X has two PRU subsystem and one of them has 6 RSIC core. If I want program the 6 core for custom function,such as UART.

How to design the AM243X chip physical pin map to the custom function pin.