Other Parts Discussed in Thread: SYSCONFIG

Note: This post is related to the prior thread.

MCU-PLUS-SDK-AM263X: Continuous sampling of multiple ADCs to DMA buffers

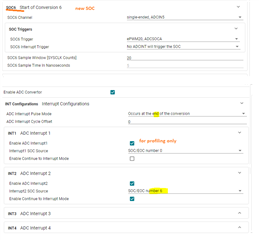

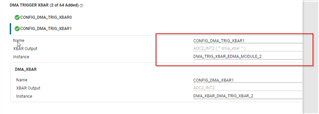

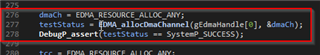

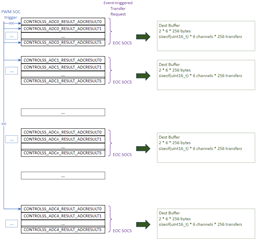

I am using EDMA to transfer ADC values from all channels of modules as seen in this diagram:

Intermittently, I see what seem to be invalid (zero) values in the destination buffer.

I need the Param Set values that I am using validated. What values (marked ?) should I be using?

EDMA Channel PaRAM Set Entry Fields

Channel Options Parameter (OPT) : (EDMA_OPT_TCINTEN_MASK |

((((uint32_t)tcc) << EDMA_OPT_TCC_SHIFT) & EDMA_OPT_TCC_MASK));

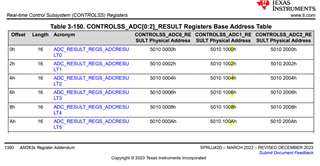

Channel Source Address (SRC) : (uint32_t) SOC_virtToPhy((void *)(adc_base+CSL_ADC_RESULT_ADCRESULT0));

Channel Destination Address (DST) : (uint32_t) SOC_virtToPhy((void *) dest_buf);

Count for 1st Dimension (ACNT) : ?

Count for 2nd Dimension (BCNT) : ?

Count for 3rd Dimension (CCNT) : ?

BCNT Reload (BCNTRLD) : ?

Source B Index (SBIDX) : ?

Destination B Index (DBIDX) : ?

Source C Index (SCIDX) : ?

Destination C Index (DCIDX) : ?

Link Address (LINK) : 0xFFFFU