Hello,

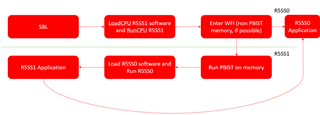

I am using AM2632 in lockstep mode, we are developing a functional safety application for R5SS0 at the moment.

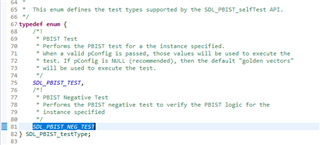

We already use the pBIST library for memory-stuckAt-tests at the run up of our system.

Now I have found the STC example in the SDK.

But I am not sure what is the test content/test aim of STC in general? The TRM is also not very detailed here and the code example does not give further information.

Can you give me some infos, what is the test focus of the STC?

Are there the core registers (R0,R1,...)...of the R5F-controller tested with STC?

Are there some tests of assembler instructions content of the STC?

Thanks and best regards

Josef Schönhuber