Part Number: AM2631

Hello,

Running the GPMC sample code of SDK (am263x_09_01_00_41), I am setting the GPMC_CLK_SRC_SEL using a GEL file before main gets to run. When reaching HwiP_enableFIQ(), the value is modified.

Is it intended?

Regards,

Javier

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: AM2631

Hello,

Running the GPMC sample code of SDK (am263x_09_01_00_41), I am setting the GPMC_CLK_SRC_SEL using a GEL file before main gets to run. When reaching HwiP_enableFIQ(), the value is modified.

Is it intended?

Regards,

Javier

Hi Javier,

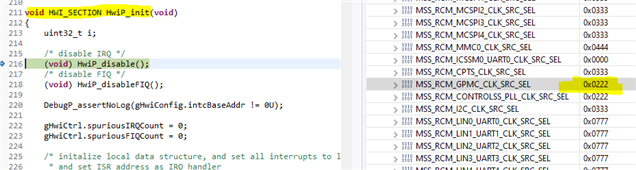

The Hwip_enableFIQ() just changes F bit of CPSR register, it doesn't change the clock source for GPMC. I think that 0x2 (system clock) is the default clock source for GPMC.

My test shows that the GPMC clock source is 0x222 before calling Hwip_enableFIQ() and after calling Hwip_enableFIQ() .

Before calling Hwip_enableFIQ():

After calling FIQ enable function:

Thanks for checking QJ,

Instead of running step-by-step, I added a watchpoint when writing to the GPMC_CLK_SRC_SEL register, and then saw that it was the setting on gSocModulesClockFrequency what was causing this change. Modifying the values within it fixes the issue.

Not sure why the CCS was showing the behavior described originally.

Having said so, this thread can be closed.

Regards,

Javier.