Hello,

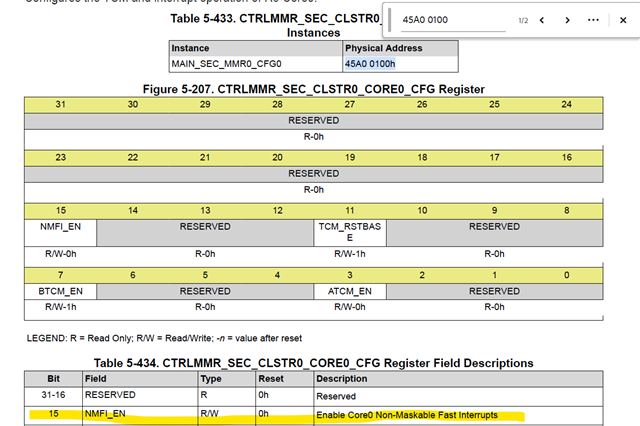

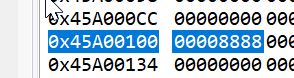

we are using the RTI DWWD in our application. I once learned that a POR-reset is not possible with this Watchdog on the AM243X. But a NMI should be possible.

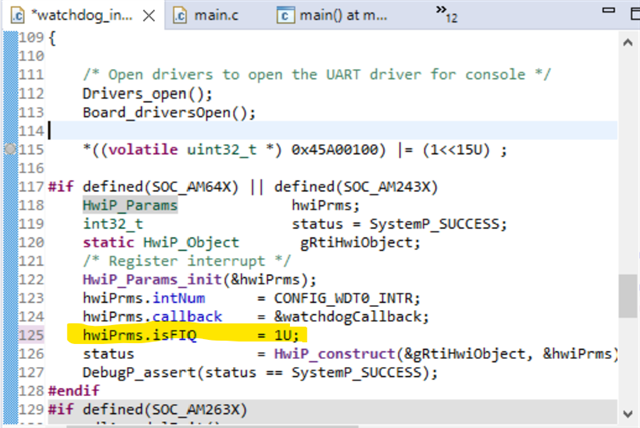

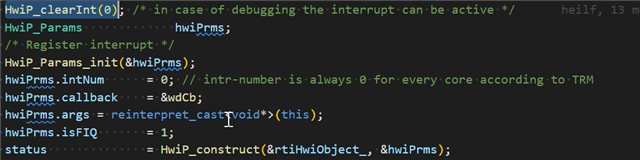

We noticed that indeed an interrupt occurs when the time-window is expiring but now we also noticed as soon as someone calls HwiP_disable() this also disables the Watchdog-interrupt. But as I understood as an NMI it should occur anyway even if the other interrupts are disabled.

We noticed that when we did hang in an assert-loop which disables the interrupts while we were expecting the watchdog to trigger, which did not happen.

Is this another limitation to the RTI DWWD?

Best regards

Felix