Other Parts Discussed in Thread: HALCOGEN

Hello,

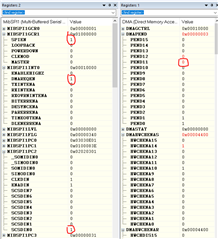

I made following observation the SPI signals; "bogus" PEND-bit is set to DMA if SPI is used in slave mode and you disable it. Can you confirm? Cannot found any remarks on such behavior from the reference manual...

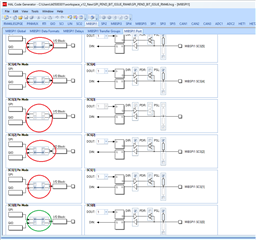

This is very trivial to try, just need to configure the DMA to be interested on SPI requests (not showing that part)

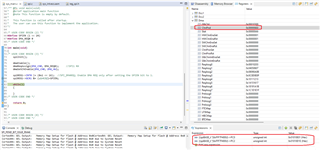

In slave mode:

// config DMA to listen requests from SPI

ptSpi->GCR1 = 0U; // disable & slave mode

ptSpi->INT0 = 0U; // remove what ever HALCoGen has set

ptSpi->INT0 |= SPI_INT0_DMAREQEN; // enable DMA

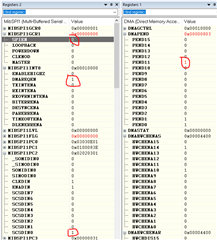

ptSpi->GCR1 |= SPI_GCR1_EN; // enable SPI -> this creates PEND for TX (as supposed to)

ptSpi->GCR1 &= (uint32)~SPI_GCR1_EN; // shut off SPI -> This creates PEND for RX channel!!!

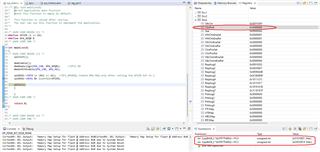

In master mode it works correctly:

// config DMA to listen requests from SPI

ptSpi->GCR1 = 0U; // disable & slave mode

ptSpi->GCR1 |= SPI_GCR1_MASTER; // enable master mode

ptSpi->INT0 = 0U; // remove what ever HALCoGen has set

ptSpi->INT0 |= SPI_INT0_DMAREQEN; // enable DMA

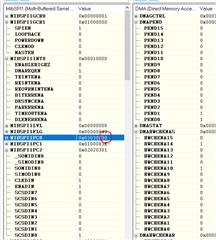

ptSpi->GCR1 |= SPI_GCR1_EN; // enable SPI -> this creates PEND for TX (as supposed to)

ptSpi->GCR1 &= (uint32)~SPI_GCR1_EN; // shut off SPI -> no PEND for RX

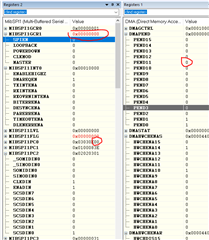

In slave mode if removing the DMAREQEN before disable then PEND for RX isn't created

...

ptSpi->INT0 &= ~SPI_INT0_DMAREQEN; // remove DMA

ptSpi->GCR1 &= (uint32)~SPI_GCR1_EN; // shut off SPI -> no PEND for RX