Part Number: LP-AM243

Other Parts Discussed in Thread: SYSCONFIG

I have created a project based on the "empty_pru_io_am243x-lp_r5fss0-0_freertos_ti-arm_clang" example, I am writing from icssg0 pru0 to msram and want to raise an interrupt from pru to r5 0-0 to signal the data is ready.

I want to be able to write to __R31 in the pru and raise an interrupt in the R5f, I've tried a variety of channels and numbers and have found combinations where the code gets stuck in the interrupt callback pru0_adc_buffer_filled_irq() and others where the interrupt never happens but not a working combination.

Could someone help me with the correct usage of the PRUICSS API and channel setup for the interrupt as I haven't found examples using PRUICSS and ideally it would be nice to understand if the constants in the sysconfig created configuration in icss0_intc_initdata can be used in the PRUICSS_registerIrqHandler() call.

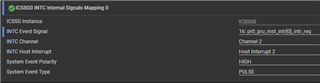

I am using sysconfig to configure intc

Which produces the following intc config

/*

* ICSSG0_INTC

*/

PRUICSS_IntcInitData icss0_intc_initdata =

{

{

ICSS_INTC_EVENT_19,

0xFF

},

{

{

ICSS_INTC_EVENT_19,

ICSS_INTC_CHANNEL_2,

SYS_EVT_POLARITY_HIGH,

SYS_EVT_TYPE_PULSE,

},

{0xFF, 0xFF, 0xFF, 0xFF}

},

{

{

ICSS_INTC_CHANNEL_2,

ICSS_INTC_HOST_INTR_2

},

{0xFF, 0xFF}

},

(

ICSS_INTC_HOST_INTR_2_HOSTEN_MASK

)

};

And modified R5f code from the example

gPruIcss0Handle = PRUICSS_open(CONFIG_PRU_ICSS0);

load_pru_firmware();

/* ... */

void load_pru_firmware(void *args)

{

/* ----------------------------------------------------------------- */

/* Program empty code on PRU Core/s; */

/* depends on usecase - might have to program multiple cores */

/* ----------------------------------------------------------------- */

/* clear ICSS PRUx data RAM */

int status;

status = PRUICSS_initMemory(gPruIcss0Handle, PRUICSS_DATARAM(PRUICSS_PRUx));

DebugP_assert(status != 0);

status = PRUICSS_resetCore(gPruIcss0Handle, PRUICSS_PRUx);

DebugP_assert(SystemP_SUCCESS == status);

status = PRUICSS_disableCore(gPruIcss0Handle, PRUICSS_PRUx);

DebugP_assert(SystemP_SUCCESS == status);

status = PRUICSS_registerIrqHandler(gPruIcss0Handle, 2, 120, 3, 0, &pru0_adc_buffer_filled_irq);

DebugP_assert(SystemP_SUCCESS == status);

status = PRUICSS_intcInit(gPruIcss0Handle, &icss0_intc_initdata);

DebugP_assert(SystemP_SUCCESS == status);

/* Load firmware. Set buffer = write to Pru memory */

status = PRUICSS_writeMemory(gPruIcss0Handle, PRUICSS_IRAM_PRU(PRUICSS_PRUx), 0,

(uint32_t *) PRUFirmware_0, sizeof(PRUFirmware_0));

DebugP_assert(status != 0);

status = PRUICSS_resetCore(gPruIcss0Handle, PRUICSS_PRUx);

DebugP_assert(SystemP_SUCCESS == status);

/* Run firmware */

status = PRUICSS_enableCore(gPruIcss0Handle, PRUICSS_PRUx);

DebugP_assert(SystemP_SUCCESS == status);

}

On the PRU

#define PRU_ARM_INTERRUPT_PULSE (0x23) /* bit 5 and channel 3, bits 3:0 */

volatile register uint32_t __R31;

/* GPI Mode 0, GPO Mode 0 */

CT_CFG.gpcfg0_reg = 0x00000000;

__R31 = PRU_ARM_INTERRUPT_PULSE;

I am not using the PRU IPC module as I am writing 64k-96k of data to the MSRAM with minimal delays, I'd also like to understand how to set up the interrupts.

There's not much else going on so I have extracted the code related to the interrupts, if full code examples are needed let me know.

Thanks for any help you can provide.