Other Parts Discussed in Thread: HALCOGEN

Hello all,

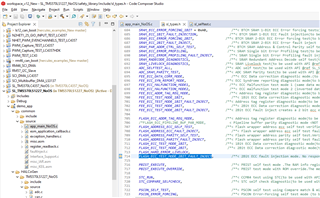

I use the the bank 7 sectors 0 to 3 as non volatile memory (EEPROM emulation). I do not use the FEE Library by provided by TI but I use my own ware leveling algorithm which I already used on other micro controllers which all works fine so far.

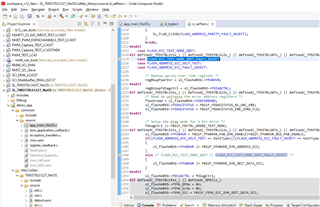

Now I want to benefit form the ECC feature. As far as I know each 64 Bit of data word is secured by 8 bit ECC. So I make sure that all data is written in multiples of 8 bytes. For the write commands I alredy use use the mode Fapi_AutoEccGeneration.

Fapi_issueProgrammingCommand((uint32_t*)u32_Addr, &(u8_Buffer[0]), u8_idx, NULL, 0, Fapi_AutoEccGeneration)

I far as I believe the ECC bits should therefore generated correctly for every write.

If I erase a complete sector, do I have to care about the ECC bit or do they also be set correctly for a erased 64 bit data word?

Fapi_issueAsyncCommandWithAddress(Fapi_EraseSector, flash_sector[Sector].start) ;

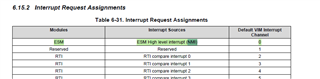

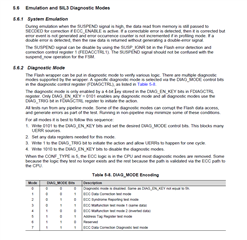

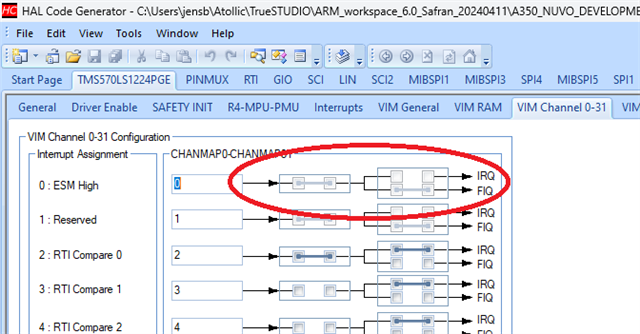

When I now want to be informed in case of a data/ecc mismatch when reading EEPROM data I need to configure the ESM.

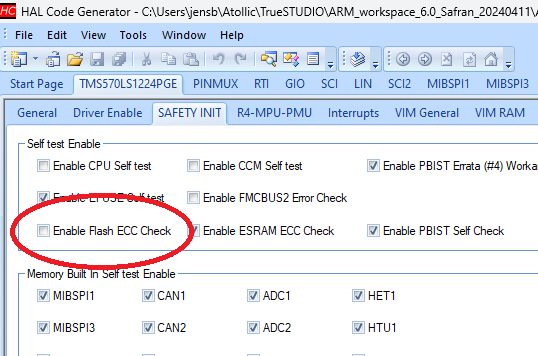

Do I also have to activate the FLASH ECC when I only want to check the EEPROM (bank 7) ECC?

And I guess I will get an ESM exception:

By the way why can't this Interrupt not be dsabled or changed to FIQ in HALCOGEN?

Is there any code Example code how to handle ESM exceptions avalable especially get the reason (ECC mismatch, including address infomation, ... ) ?

Kind regards

Jens