Part Number: AM2634-Q1

Hello,

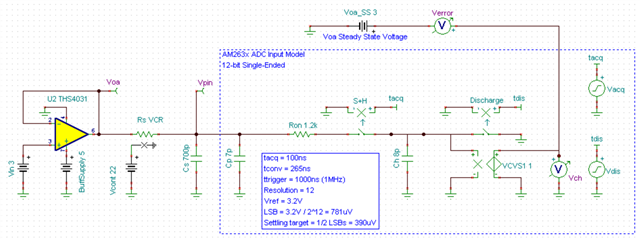

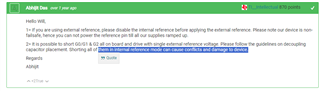

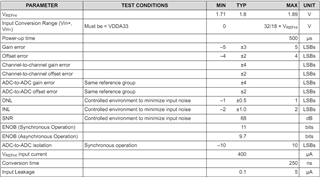

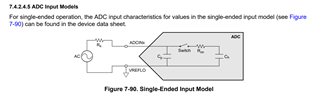

can you please direct me to where I can find the ADC input model for AM2634COKFHMZCZRQ1. It's mentioned on the reference manual that the values can be found on the datasheets, but I couldn't locate it.

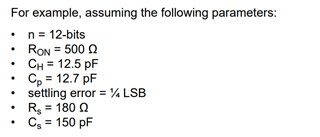

Should I use the Ron and Ch values used in the example given in page 491 of the reference manual ?

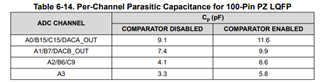

can you provide the table for the pin capacitance for each of the analogue inputs ?

Thanks,

Yassine