I am working on ADC12_0 and here is details of it:

ADC Clock Source: SYSOSC

ADC Clock Frequency 31.00MHz

Sample Clock Divider: Divide by 8

Calculated Sample Clock Frequency: 4.00 MHz

Conversion Mode: Single

Repeat Mode Enabled

Input Channel: Channel_0 (PA27)

Reference Voltage: VDDA 3.3Volt

Desired Sample Time 0 : 250uSec

Enable Interrupts: MEM0 result loaded interrupt

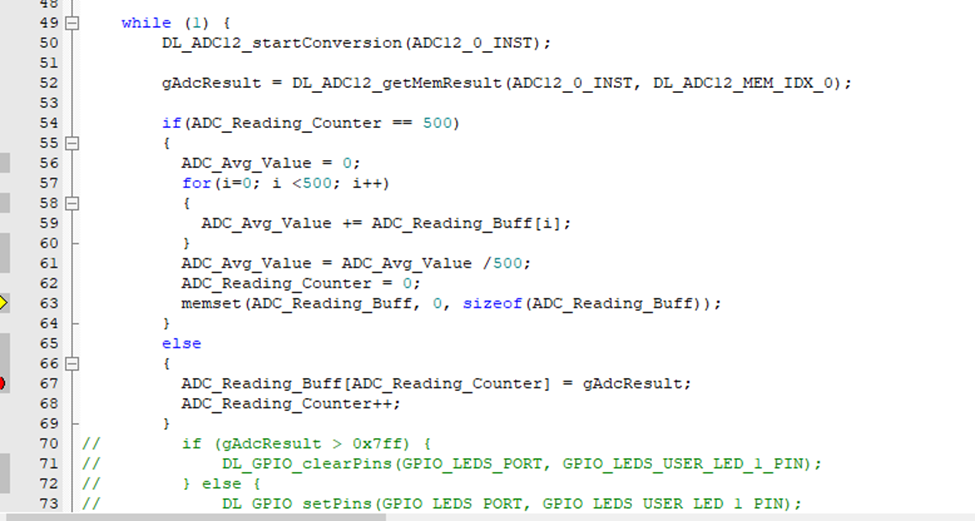

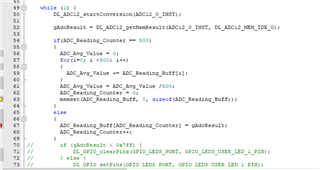

Kindly check the following code on which i am monitoring ADC values.

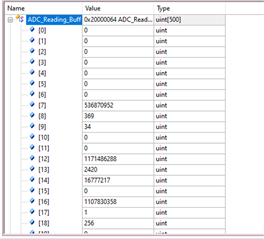

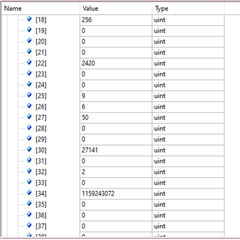

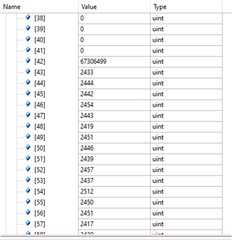

The fluctuation of values you can see clearly on attached pictures.

(for same VDDA values are completely different u can check that on attached excel sheet on column B and C) Column C values are expected output and column B is incorrect one.

|

and sometimes values What I am getting for same code same input voltage is as below

Hope this data to explain my problem is sufficient from my side.

Hoping proper answer from your side.