Part Number: LP-AM243

Hi!

I tried to,

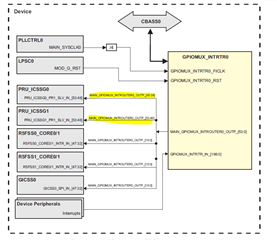

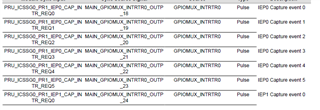

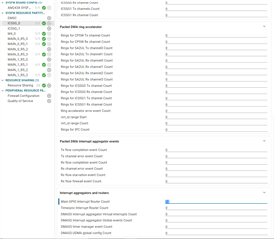

route GPIO1_0 interrupt -> MAIN_GPIOMUX_INTROUTER0_OUTP_18

MAIN_GPIOMUX_INTROUTER0_OUTP_18 -> IEP_CAP

and similarly GPIO1_1 and GPIO1_2 interrupts to MAIN_GPIOMUX_INTROUTER0_OUTP_19 and MAIN_GPIOMUX_INTROUTER0_OUTP_20 respectively

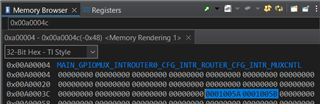

in a PRU code and it didn't work. Then I realized that GPIOMUX_INTRTR0_MUXCNTL_n must be modified via SCI client.

Therefore, I have pinmux, interrupt and IEP settings in the same PRU code and tried to configure interrupt router within an empty ARM project.

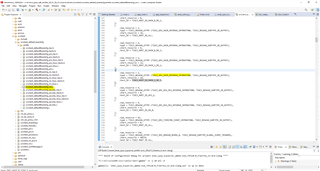

Below is my ARM code,

main.c

#include <stdlib.h>

#include <stdio.h>

#include <drivers/sciclient.h>

#include <drivers/hw_include/am64x_am243x/cslr_intr_pru_icssg0.h>

#define TISCI_DEV_GPIO1 78U

#define TISCI_BANK_SRC_IDX_BASE_GPIO1 (90U)

#define TISCI_DEV_PRU_ICSSG0 81U

int main(void)

{

int32_t retVal;

struct tisci_msg_rm_irq_set_req rmIrqReq;

struct tisci_msg_rm_irq_set_resp rmIrqResp;

rmIrqReq.valid_params = 0U;

rmIrqReq.valid_params |= TISCI_MSG_VALUE_RM_DST_ID_VALID;

rmIrqReq.valid_params |= TISCI_MSG_VALUE_RM_DST_HOST_IRQ_VALID;

rmIrqReq.global_event = 0U;

rmIrqReq.src_id = TISCI_DEV_GPIO1;

rmIrqReq.src_index = TISCI_BANK_SRC_IDX_BASE_GPIO1 + (((uint32_t) 0) >> 4U);

rmIrqReq.dst_id = TISCI_DEV_PRU_ICSSG0;

rmIrqReq.dst_host_irq = CSLR_PRU_ICSSG0_PR1_IEP0_CAP_INTR_REQ_MAIN_GPIOMUX_INTROUTER0_OUTP_18;

rmIrqReq.ia_id = 0U;

rmIrqReq.vint = 0U;

rmIrqReq.vint_status_bit_index = 0U;

rmIrqReq.secondary_host = TISCI_MSG_VALUE_RM_UNUSED_SECONDARY_HOST;

retVal = Sciclient_rmIrqSet(&rmIrqReq, &rmIrqResp, SystemP_WAIT_FOREVER);

return 0;

}

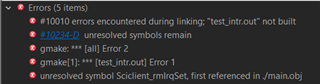

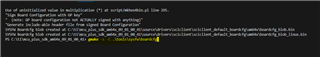

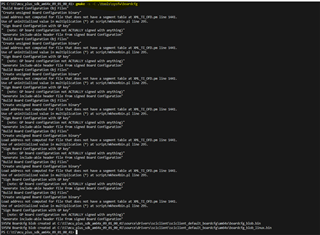

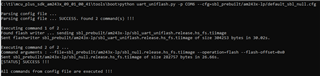

When the above code is built, it shows 5 errors. Please refer the attachment.

Please help me to solve the errors, and is my approach right?

Best regards.