While debugging my application of 4 processors with IPC, I occasionally have problems with IpcNotify functions and Spinlocks.

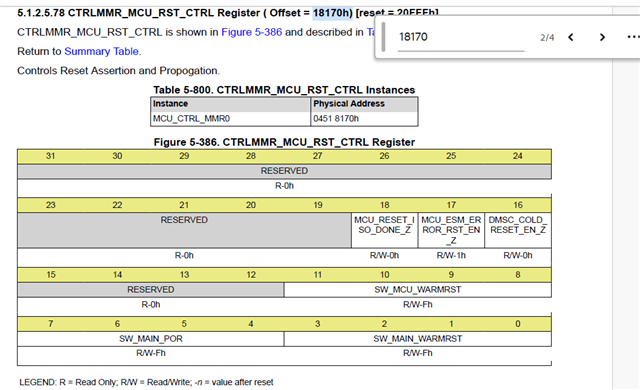

The evidence points to the state of Mailbox and Spinlocks not being reset on warm reset by the initialization functions. This makes sense to me as the right way to do it.

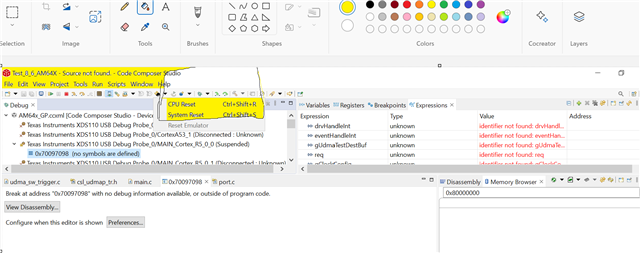

However, it makes CCS debugging a more difficult. Is there a way CCS can reset the system IPC when it resets the processors?