Part Number: AM2431

Other Parts Discussed in Thread: LP-AM243

Hi all TI experts,

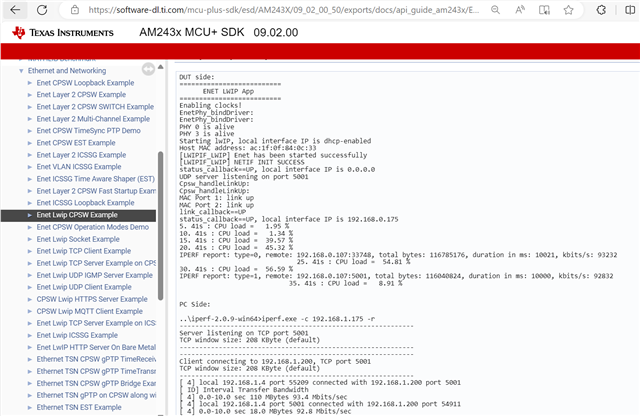

My current product uses the AM2431 as the main chip, and the SDK I am using is mcu_plus_sdk_am243x_09_01_00_41. I referred to the enet_layer2_cpsw sample program and modified it for our application.

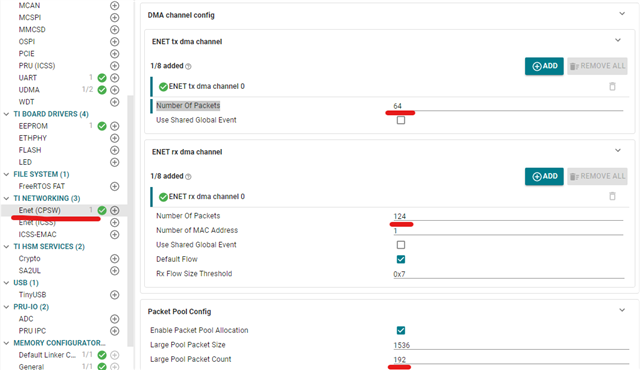

Recently, I encountered an issue where the system functions normally with only a few Ethernet packets, but when a large volume of packets is present, errors occur. I discovered that the issue is related to the configuration settings in Enet (CPSW) -> ENET RX DMA channel > Packet Pool Config. The maximum setting for the Large Pool Packet Count is 192, but my system sends 807 packets within 8 ms, each packet being 1461 bytes. After transmission, there's an idle period of about 20 ms, allowing the MCU to process the packets. Observations using Wireshark show that the data rate is approximately 125 Mbps, and given the AM2431's capability to handle gigabit Ethernet, it should theoretically manage this workload. However, it appears that the volume of packets is too great, and there isn't enough DMA space to handle them all. I am looking for any suggestions on how to resolve this issue. Thank you!

Best,

Larry