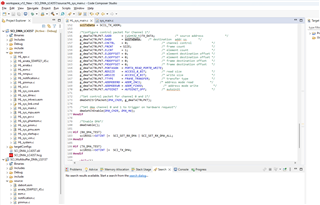

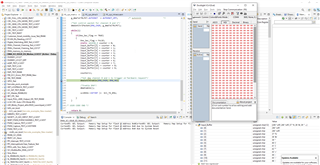

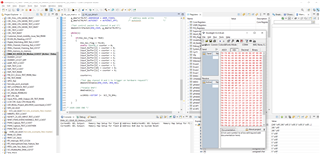

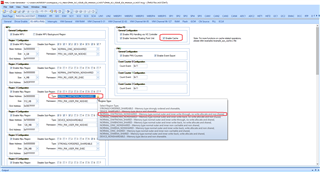

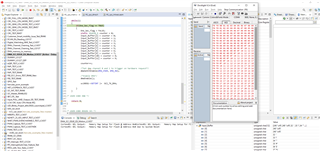

I am implementing SCI transfers using DMA, which was based on the example_sci_dma.c example file. I can (hardware) trigger the correct number of bytes to be transferred periodically, however the content of the transmit packet remains a constant. I have verified in the debugger that the DMA destination address is the correct address of the SCI-transmit-buffer, yet DMA repeatedly transfers the value of the transmit-buffer when DMA was initialized. In other words, when I initialize the DMA registers, the SCI-TX buffer is {1,2,3,4,5,6,7,8,9}, and only this data is transmitted via SCI -- even though the SCI-TX-memory has changed.

I am triggering my DMA transfer by: dmaREG->HWCHENAS = 1 (for DMA_CH0). Is there something else I have to do to cause the internal DMA memory/FIFO to be updated?

Thanks,

Jim