Other Parts Discussed in Thread: MSPM0G3507

Hi Champ,

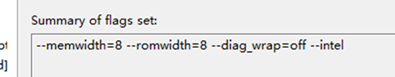

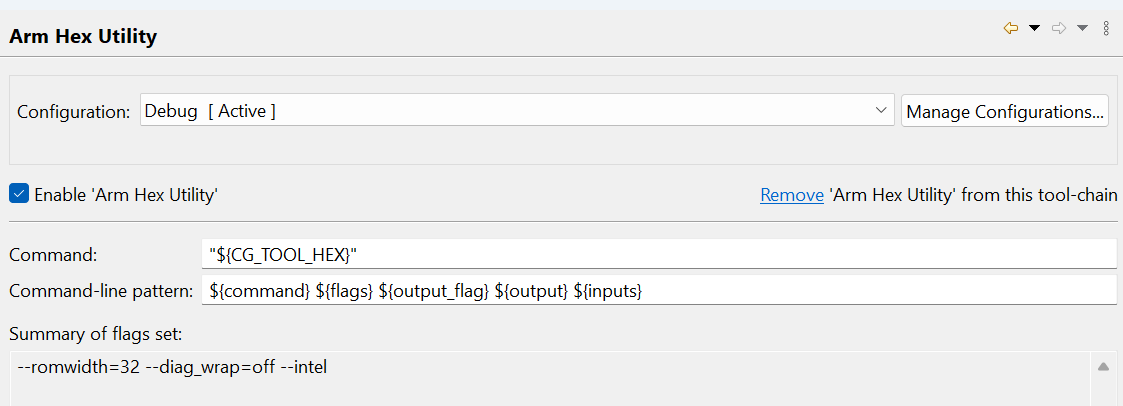

For current HEX format, the address type is 0x02-- Extended Segment Address Records, customer request is 0x04-- Extended Linear Address Records.

Could you advise the solution to generate the HEX with 0x04 address type ?

Thanks!