Hi BU experts,

My customer is developing Ethernet/IP application using am243x and dp83822. The EIP works well normally, however, when they toggle the power quickly as a stress test, the EIP connection fails.

They can't any response from the their board to the EIP host.

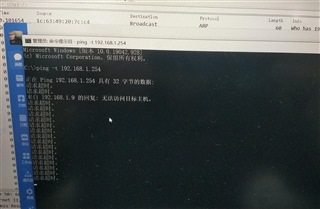

Below is a few more observation, when the device is abnormal:

1. Auto-nego becomes 10M, instead of 100M

2. In PRU register, RX good is 0

3 EIP host (PC) is not able to ping the device

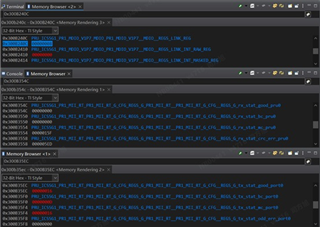

4. PHY registers are as below:

异常时 MAIN_Cortex_R5_0_0: GEL Output: ICSSG0 PHY0 Registers MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x00000003 Reg : 0x00000000 Val : 0x00003100 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x00000003 Reg : 0x00000001 Val : 0x0000786D MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x00000003 Reg : 0x00000002 Val : 0x00002000 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x00000003 Reg : 0x00000003 Val : 0x0000A240 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x00000003 Reg : 0x00000004 Val : 0x000001E1 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x00000003 Reg : 0x00000005 Val : 0x0000CC61 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x00000003 Reg : 0x00000006 Val : 0x0000000D MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x00000003 Reg : 0x00000007 Val : 0x00002001 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x00000003 Reg : 0x00000008 Val : 0x00005806 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x00000003 Reg : 0x00000009 Val : 0x00000000 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x00000003 Reg : 0x0000000A Val : 0x00000100 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x00000003 Reg : 0x0000000B Val : 0x00001000 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x00000003 Reg : 0x0000000C Val : 0x00000000 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x00000003 Reg : 0x0000000D Val : 0x0000401F MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x00000003 Reg : 0x0000000E Val : 0x00000000 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x00000003 Reg : 0x0000000F Val : 0x00000000 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x00000003 Reg : 0x00000010 Val : 0x00000017 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x00000003 Reg : 0x00000011 Val : 0x00000108 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x00000003 Reg : 0x00000012 Val : 0x00000000 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x00000003 Reg : 0x00000013 Val : 0x00000000 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x00000003 Reg : 0x00000014 Val : 0x00000000 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x00000003 Reg : 0x00000015 Val : 0x00000000 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x00000003 Reg : 0x00000016 Val : 0x00000100 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x00000003 Reg : 0x00000017 Val : 0x00000049 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x00000003 Reg : 0x00000018 Val : 0x00000400 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x00000003 Reg : 0x00000019 Val : 0x00008003 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x00000003 Reg : 0x0000001A Val : 0x00000000 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x00000003 Reg : 0x0000001B Val : 0x0000007D MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x00000003 Reg : 0x0000001C Val : 0x000005EE MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x00000003 Reg : 0x0000001D Val : 0x00000000 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x00000003 Reg : 0x0000001E Val : 0x00000002 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x00000003 Reg : 0x0000001F Val : 0x00000000 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x00000003 Reg : 0x00000042 Val : 0x00000000 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x00000003 Reg : 0x00000467 Val : 0x00003F4F MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x00000003 Reg : 0x00000468 Val : 0x00000000 MAIN_Cortex_R5_0_0: GEL Output: ICSSG0 PHY1 Registers MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x0000000F Reg : 0x00000000 Val : 0x00003100 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x0000000F Reg : 0x00000001 Val : 0x00007849 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x0000000F Reg : 0x00000002 Val : 0x00002000 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x0000000F Reg : 0x00000003 Val : 0x0000A240 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x0000000F Reg : 0x00000004 Val : 0x000001E1 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x0000000F Reg : 0x00000005 Val : 0x00000000 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x0000000F Reg : 0x00000006 Val : 0x00000004 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x0000000F Reg : 0x00000007 Val : 0x00002001 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x0000000F Reg : 0x00000008 Val : 0x00000000 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x0000000F Reg : 0x00000009 Val : 0x00000000 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x0000000F Reg : 0x0000000A Val : 0x00000100 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x0000000F Reg : 0x0000000B Val : 0x00001000 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x0000000F Reg : 0x0000000C Val : 0x00000000 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x0000000F Reg : 0x0000000D Val : 0x0000401F MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x0000000F Reg : 0x0000000E Val : 0x00000003 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x0000000F Reg : 0x0000000F Val : 0x00000000 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x0000000F Reg : 0x00000010 Val : 0x00004002 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x0000000F Reg : 0x00000011 Val : 0x00000108 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x0000000F Reg : 0x00000012 Val : 0x00000000 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x0000000F Reg : 0x00000013 Val : 0x00000000 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x0000000F Reg : 0x00000014 Val : 0x00000000 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x0000000F Reg : 0x00000015 Val : 0x00000000 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x0000000F Reg : 0x00000016 Val : 0x00000100 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x0000000F Reg : 0x00000017 Val : 0x00000041 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x0000000F Reg : 0x00000018 Val : 0x00000400 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x0000000F Reg : 0x00000019 Val : 0x0000800F MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x0000000F Reg : 0x0000001A Val : 0x00000000 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x0000000F Reg : 0x0000001B Val : 0x0000007D MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x0000000F Reg : 0x0000001C Val : 0x000005EE MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x0000000F Reg : 0x0000001D Val : 0x00000000 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x0000000F Reg : 0x0000001E Val : 0x00000102 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x0000000F Reg : 0x0000001F Val : 0x00000000 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x0000000F Reg : 0x00000042 Val : 0x00000000 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x0000000F Reg : 0x00000467 Val : 0x0000FF4F MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x0000000F Reg : 0x00000468 Val : 0x00000003

正常时 MAIN_Cortex_R5_0_0: GEL Output: CPU reset (soft reset) has been issued through GEL. MAIN_Cortex_R5_0_0: GEL Output: ICSSG0 PHY0 Registers MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x00000003 Reg : 0x00000000 Val : 0x00003100 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x00000003 Reg : 0x00000001 Val : 0x0000786D MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x00000003 Reg : 0x00000002 Val : 0x00002000 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x00000003 Reg : 0x00000003 Val : 0x0000A240 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x00000003 Reg : 0x00000004 Val : 0x000001E1 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x00000003 Reg : 0x00000005 Val : 0x0000CDE1 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x00000003 Reg : 0x00000006 Val : 0x0000000F MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x00000003 Reg : 0x00000007 Val : 0x00002001 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x00000003 Reg : 0x00000008 Val : 0x00004006 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x00000003 Reg : 0x00000009 Val : 0x00000000 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x00000003 Reg : 0x0000000A Val : 0x00000100 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x00000003 Reg : 0x0000000B Val : 0x00001000 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x00000003 Reg : 0x0000000C Val : 0x00000000 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x00000003 Reg : 0x0000000D Val : 0x00000000 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x00000003 Reg : 0x0000000E Val : 0x00000000 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x00000003 Reg : 0x0000000F Val : 0x00000000 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x00000003 Reg : 0x00000010 Val : 0x00000615 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x00000003 Reg : 0x00000011 Val : 0x00000108 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x00000003 Reg : 0x00000012 Val : 0x00006400 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x00000003 Reg : 0x00000013 Val : 0x00002800 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x00000003 Reg : 0x00000014 Val : 0x00000000 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x00000003 Reg : 0x00000015 Val : 0x00000000 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x00000003 Reg : 0x00000016 Val : 0x00000100 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x00000003 Reg : 0x00000017 Val : 0x00000049 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x00000003 Reg : 0x00000018 Val : 0x00000400 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x00000003 Reg : 0x00000019 Val : 0x00008C03 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x00000003 Reg : 0x0000001A Val : 0x00000000 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x00000003 Reg : 0x0000001B Val : 0x0000007D MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x00000003 Reg : 0x0000001C Val : 0x000005EE MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x00000003 Reg : 0x0000001D Val : 0x00000000 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x00000003 Reg : 0x0000001E Val : 0x00000102 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x00000003 Reg : 0x0000001F Val : 0x00000000 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x00000003 Reg : 0x00000042 Val : 0x00000000 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x00000003 Reg : 0x00000467 Val : 0x00003F4F MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x00000003 Reg : 0x00000468 Val : 0x00000000 MAIN_Cortex_R5_0_0: GEL Output: ICSSG0 PHY1 Registers MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x0000000F Reg : 0x00000000 Val : 0x00003100 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x0000000F Reg : 0x00000001 Val : 0x00007849 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x0000000F Reg : 0x00000002 Val : 0x00002000 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x0000000F Reg : 0x00000003 Val : 0x0000A240 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x0000000F Reg : 0x00000004 Val : 0x000001E1 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x0000000F Reg : 0x00000005 Val : 0x00000000 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x0000000F Reg : 0x00000006 Val : 0x00000004 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x0000000F Reg : 0x00000007 Val : 0x00002001 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x0000000F Reg : 0x00000008 Val : 0x00000000 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x0000000F Reg : 0x00000009 Val : 0x00000000 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x0000000F Reg : 0x0000000A Val : 0x00000100 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x0000000F Reg : 0x0000000B Val : 0x00001000 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x0000000F Reg : 0x0000000C Val : 0x00000000 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x0000000F Reg : 0x0000000D Val : 0x00000000 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x0000000F Reg : 0x0000000E Val : 0x00000000 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x0000000F Reg : 0x0000000F Val : 0x00000000 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x0000000F Reg : 0x00000010 Val : 0x00000002 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x0000000F Reg : 0x00000011 Val : 0x00000108 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x0000000F Reg : 0x00000012 Val : 0x00000000 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x0000000F Reg : 0x00000013 Val : 0x00000800 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x0000000F Reg : 0x00000014 Val : 0x00000000 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x0000000F Reg : 0x00000015 Val : 0x00000000 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x0000000F Reg : 0x00000016 Val : 0x00000100 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x0000000F Reg : 0x00000017 Val : 0x00000041 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x0000000F Reg : 0x00000018 Val : 0x00000400 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x0000000F Reg : 0x00000019 Val : 0x0000800F MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x0000000F Reg : 0x0000001A Val : 0x00000000 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x0000000F Reg : 0x0000001B Val : 0x0000007D MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x0000000F Reg : 0x0000001C Val : 0x000005EE MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x0000000F Reg : 0x0000001D Val : 0x00000000 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x0000000F Reg : 0x0000001E Val : 0x00000102 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x0000000F Reg : 0x0000001F Val : 0x00000000 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x0000000F Reg : 0x00000042 Val : 0x00000000 MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x0000000F Reg : 0x00000467 Val : 0x0000FF4F MAIN_Cortex_R5_0_0: GEL Output: PhyAddr: 0x0000000F Reg : 0x00000468 Val : 0x00000003

5. When the device is abnormal, re-connecting the cable would not restore connection, but another power cycle will do.

Is there any suggestion on how to locate the issue?

Regards,

Hang.