Other Parts Discussed in Thread: BQ76952

Hi,

Background:

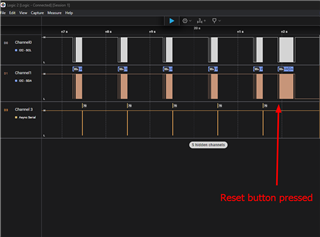

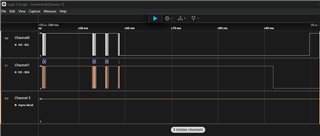

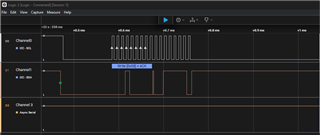

I am currently working with a custom board that features an MSPM0L1305 as the main MCU, communicating with two BQ76952 chips via I2C. Upon resetting the MCU, I sometimes observe the I2C bus getting stuck low, causing the program to hang indefinitely while waiting to exit the "bus busy" state. The I2C bus only recovers when I completely reset the BQ76952 chips by disconnecting and reconnecting the power.

Question:

Is there any way the host MCU can inform the targets (BQ76952) to release the bus in this situation?

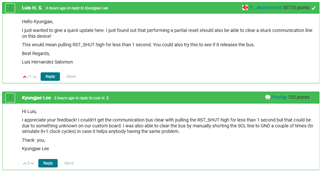

I was informed that the controller generating 9-10 scl cycles will do the trick. If this is a recommended solution, can you please provide the correct way to generate a certain number of clock cycles?

Thank you,

Kyungjae Lee