Other Parts Discussed in Thread: LAUNCHXL2-570LC43, HALCOGEN

Tool/software:

Observe a strange behavior of N2HET device on LAUNCHXL2-570LC43.

In pooling mode, at rate 5 ms, it captured correct period value after boot. Then after 2 to 5 min, period value doble, and it continue in this state till you reset controller. Always repeatable for input square from 100 - 4 kHz.

What can be a reason?

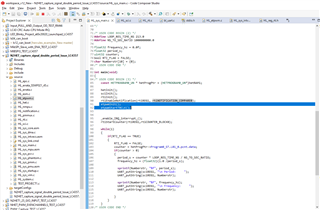

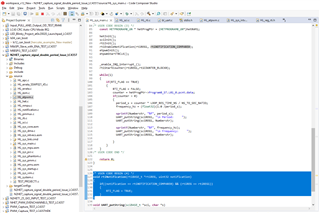

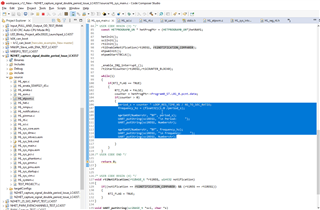

N2HET code:

Assembly code from HET Ide:

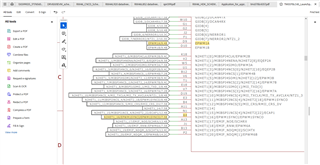

; Use PCNT to measure period on 4 pins

L00 PCNT { type=FALL2FALL,pin=11,control=ON,period=0};

L01 PCNT { type=FALL2FALL,pin=16,control=ON,period=0};

L02 PCNT { type=FALL2FALL,pin=23,control=ON,period=0};

L03 PCNT { type=FALL2FALL,pin=31,control=ON,period=0};

; Used to wait for the next iteration of the loop

L04 BR { next=L00, cond_addr=L00, event=NOCOND};

HET_MEMORY const HET_INIT0_PST[5] =

{

/* L00_0 */

{

0x00002E8B,

0x04000000,

0x00000000,

0x00000000

},

/* L01_0 */

{

0x00004E90,

0x04000000,

0x00000000,

0x00000000

},

/* L02_0 */

{

0x00006E97,

0x04000000,

0x00000000,

0x00000000

},

/* L03_0 */

{

0x00008E9F,

0x04000000,

0x00000000,

0x00000000

},

/* L04_0 */

{

0x00001A00,

0x00000000,

0x00000000,

0x00000000

}

};

Configuration:

Halcogen:

Generated:

void hetInit(void)

{

/** @b initialize @b HET */

/** - Set HET pins default output value */

hetREG1->DOUT = (uint32)((uint32)0U << 31U)

| (uint32)((uint32)0U << 30U)

| (uint32)((uint32)0U << 29U)

| (uint32)((uint32)0U << 28U)

| (uint32)((uint32)0U << 27U)

| (uint32)((uint32)0U << 26U)

| (uint32)((uint32)0U << 25U)

| (uint32)((uint32)0U << 24U)

| (uint32)((uint32)0U << 23U)

| (uint32)((uint32)0U << 22U)

| (uint32)((uint32)0U << 21U)

| (uint32)((uint32)0U << 20U)

| (uint32)((uint32)0U << 19U)

| (uint32)((uint32)0U << 18U)

| (uint32)((uint32)0U << 17U)

| (uint32)((uint32)0U << 16U)

| (uint32)((uint32)0U << 15U)

| (uint32)((uint32)0U << 14U)

| (uint32)((uint32)0U << 13U)

| (uint32)((uint32)0U << 12U)

| (uint32)((uint32)0U << 11U)

| (uint32)((uint32)0U << 10U)

| (uint32)((uint32)0U << 9U)

| (uint32)((uint32)0U << 8U)

| (uint32)((uint32)0U << 7U)

| (uint32)((uint32)0U << 6U)

| (uint32)((uint32)0U << 5U)

| (uint32)((uint32)0U << 4U)

| (uint32)((uint32)0U << 3U)

| (uint32)((uint32)0U << 2U)

| (uint32)((uint32)0U << 1U)

| (uint32)((uint32)0U << 0U);

/** - Set HET pins direction */

hetREG1->DIR = (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U;

/** - Set HET pins open drain enable */

hetREG1->PDR = (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U;

/** - Set HET pins pullup/down enable */

hetREG1->PULDIS = (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U;

/** - Set HET pins pullup/down select */

hetREG1->PSL = (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U;

/** - Set HET pins high resolution share */

hetREG1->HRSH = (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U;

/** - Set HET pins AND share */

hetREG1->AND = (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U;

/** - Set HET pins XOR share */

hetREG1->XOR = (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U;

/* USER CODE BEGIN (1) */

/* USER CODE END */

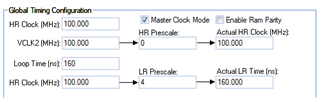

/** - Setup prescaler values

* - Loop resolution prescaler

* - High resolution prescaler

*/

hetREG1->PFR = (uint32)((uint32) 4U << 8U)

| ((uint32) 0U);

/** - Parity control register

* - Enable/Disable Parity check

*/

hetREG1->PCR = (uint32) 0x00000005U;

/** - Fill HET RAM with opcodes and Data */

/** - "x" in "HET_INITx_PST" denote the HET module Instance

* Valid range of x - 0 to 9

* For HET1 module x = 0

* Refer HET assembler User guide for more Info

*/

/*SAFETYMCUSW 94 S MR:11.1,11.2,11.4 <APPROVED> "HET RAM Fill from the table - Allowed as per MISRA rule 11.2" */

/*SAFETYMCUSW 95 S MR:11.1,11.4 <APPROVED> "HET RAM Fill from the table - Allowed as per MISRA rule 11.2" */

/*SAFETYMCUSW 95 S MR:11.1,11.4 <APPROVED> "HET RAM Fill from the table - Allowed as per MISRA rule 11.2" */

(void)memcpy((void*)hetRAM1, (void*)HET_INIT0_PST, sizeof(HET_INIT0_PST));

/** - Setup interrupt priority level */

hetREG1->PRY = 0xFFFFFFFF;

/** - Enable interrupts */

hetREG1->INTENAC = 0xFFFFFFFFU;

hetREG1->INTENAS = (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U

| (uint32) 0x00000000U;

/** - Setup control register

* - Enable output buffers

* - Ignore software breakpoints

* - Master or Slave Clock Mode

* - Enable HET

*/

hetREG1->GCR = ( 0x00000001U

| (uint32)((uint32)0U << 24U)

| (uint32)((uint32)1U << 16U)

| (0x00020000U));

/* USER CODE BEGIN (4) */

/* USER CODE END */

}