Tool/software:

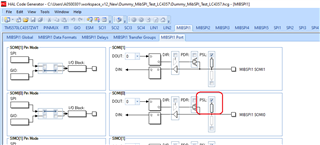

Hi, I'm using the TMS570LS3137 MIBSPI5 as a slave. We are transferring 7 16-bit words in one transfer group (single Chip Select assertion) frame.

Each SPI transfer the Slave is transmitting 7 16-bits of Slave status and receiving 7 16-bits of new commands from the Master.

The Master controls the SPI transactions timing and the transactions are asynchronous to the Slave regularly updating the TXRAM buffers using mibspiSetData().

We have a concern about what happens when the Master sends a SPI transaction in the middle of the the Slave updating the 7 data words in TXRAM buffers.

We are worried that the first 3 16-bit words could be sent from the Slave to the Master then the Slave status data is updated and the following 4 words of the frame might not be coherent with the first 3 words of the Slave status transmit data.

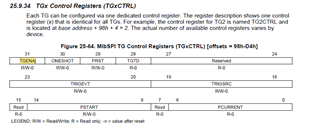

While it appears that each 16 bit word is moved into the TX shift register (per Section 25.2.2.1 of the TMS570LS31x/21x 16/32-Bit RISC Flash Microcontroller Technical Reference Manual, see below) in a single operation, how can we ensure our 7 16-bit Slave transmit transfer group is transferred as one coherent block of data?

Thanks,

-Joe

______________________

25.2.2.1 Data Sequencing when SPIDAT0 or SPIDAT1 is Written

• If both the TX shift register and TXBUF are empty, then the data is directly copied to the TX shift

register. For devices with DMA, if DMA is enabled, a transmit DMA request (TX_DMA_REQ) is

generated to cause the next word to be fetched. If transmit interrupts are enabled, a transmitter-empty

interrupt is generated.

• If the TX shift register is already full or is in the process of shifting and if TXBUF is expty then the data

written to SPIDAT0 / SPIDAT1 is copied to TXBUF and TXFULL flag is set to 1 at the same time.

• When a shift operation is complete, data from the TXBUF (if it is full) is copied into TX shift register

and the TXFULL flag is cleared to 0 to indicate that next data can be fetched. A transmit DMA request

(if enabled) or a transmitter-empty interrupt (if enabled) is generated at the same time.