Other Parts Discussed in Thread: EK-TM4C1294XL

Tool/software: Code Composer Studio

Hi everyone,

I'm currently working on a project that involves using Quad SPI (QSPI) communication in DMA mode. I'm looking for any articles, tutorials, or documentation that specifically cover this topic.

- Configuration and setup for DMA mode in QSPI.

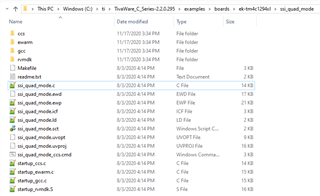

- Code examples or sample projects demonstrating QSPI with DMA.

- Common pitfalls and troubleshooting tips for QSPI in DMA mode.

If anyone can point me to relevant resources or share their own experiences, I would greatly appreciate it.

Thanks in advance for your help!