Part Number: TMS470R1B768

Other Parts Discussed in Thread: TMS570LC4357

Tool/software:

Dear TI Team,

Hello it's Maryam business development of Rotech-Group, I hope this email finds you well. I am currently working on designing an open-source RISC-V processor. As part of this project, I am in need of a JTAG IP module for debugging purposes to fabricate beside my processor.

After researching available options, I came across your company's JTAG IP module, and I am impressed by its features and compatibility with RISC-V architectures. I believe that your module would be an excellent fit for my project.

Could you please provide me with the following information:

1. Pricing details for the JTAG or SW-DP IP module (in verilog or vhdl format for ASIC design flow )

2. Licensing terms (e.g., perpetual license, subscription-based)

3. Technical documentation or user guide

4. Availability and estimated delivery time

Additionally, if there are any evaluation licenses or trial versions available, I would appreciate the opportunity to test the module before making a final decision.

Thank you for your attention to this matter. I look forward to hearing from you soon.

Best regards

Maryam

Website: www.rotech-group.com

Phone number/WeChat/WhatsApp: 008613122402442

-----------------------------------------

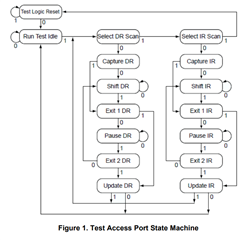

AS an Electronic engineer that designs CPU core architecture I need IEEE 1149.1 JTAG BOUNDARY SCAN IP MODULE in verilog or vhdl format to fabricate with my CPU core that supports jtag port

Please receive attached file.

I circled the item that I want with red line.

Looking forward to hear from you