Tool/software:

Hi,

Kindly confirm the connection of EMIF address lines for External Flash U2 and SRAM U3 in attached schematic diagram.

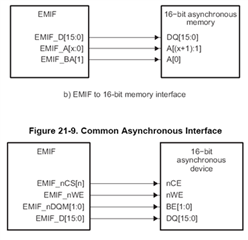

As per the Reference Manual Figure 21.8 The conneection for 16 bit Memory is different. ie. EMIF ADD 0 shall be connected to memory ADD1.

Kindly confirm.  EMIF_16Bit_.pdf

EMIF_16Bit_.pdf