Other Parts Discussed in Thread: SYSCONFIG

Tool/software:

Hi,

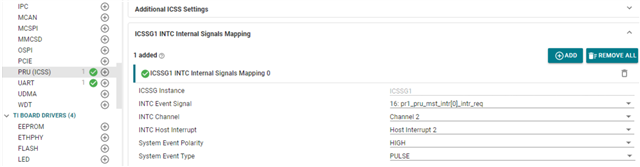

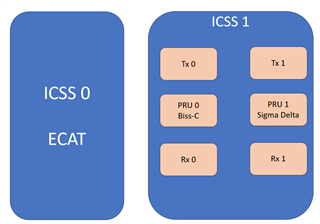

I would like to kindly request an example project with both the biss-c application and the sigma delta application running on the same PRU (ICSS 1).

1. Sigma Delta -

a. ICSS 1

b. Slice: 1

c. Core: PRU (PRU 1)

2. Biss-C:

a. ICSS 1

b. Slice: 0

c. Core: PRU (PRU 0)

Please note: Our product will run the ECAT project on ICSS 0

Thanks,

Ariel