Part Number: TM4C1237H6PZ

Tool/software:

Hi,

I'm dealing with a hard fault which currently prevents me from being able to validate the application.

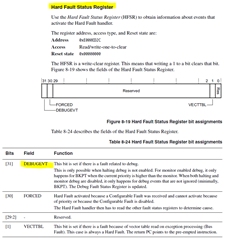

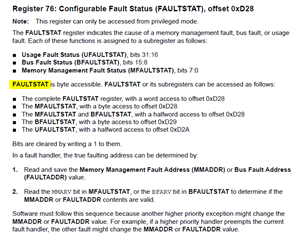

At each reset the FAULT_STAT register is all zero.

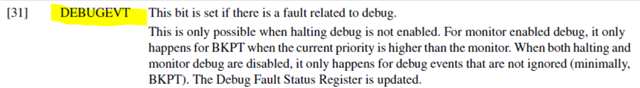

Instead, the HARD FAULT STAT register is always at zero, but when the ISR hard fault is triggered the DBG bit is at 1 (only that).

In the datasheet it is written that the bit is reserved for DEBUG but the application is not in debug.

And I can't find additional information for this type of hard fault.

I therefore ask if you can elaborate on the meaning of this bit, and the possible causes of it

Set to 1.

Looking forward to your kind reply,

Best regards.