Tool/software:

TI Expert:

I have some questions regarding SDL on the AM2432:

In Section 6.2.3.7 of the TRM, it states about the R5FSS ECC aggregator: "Note that because the R5FSS ECC aggregator is only used in error-injection mode, it only supports a subset of the generic ECC aggregator functionality in the device."

My questions are as follows:

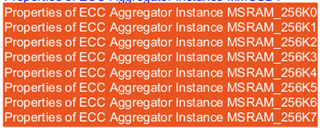

1. Since the R5FSS ECC aggregator is only used in error-injection mode, which ECC aggregator is employed for Memory ECC diagnostic measures in the Security Manual when implemented? What is the required memory sub-type initialization?

2. Which ECC aggregator is utilized for Memory ECC diagnostic measures on-chip SRAM under normal conditions? And which aggregator would be used to inject errors if needed?

3. In what circumstances is the SDL_ECC_AGGR1 aggregator employed?

4. Which ESM event source is generated by the CBA4 - Override register parity diagnostic measure?

Looking forward to your response, best regards.