Part Number: MCU-PLUS-SDK-AM263X

Other Parts Discussed in Thread: AM2634

Tool/software:

Hi

Trying to run the spinlock example from project wizard (sdk is MCU+ SDK for AM263x 9.2.0.56)

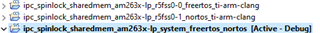

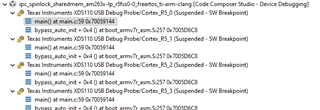

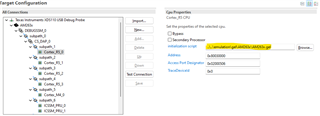

1. I can get to this point with 4 cores only after a full reset of the devboard (on stopping and restarting debug I can't, only core1 has the breakpoint in main, the other 3 are running by default - probably core 1,2,3 hangs from previous run).

I have seen this thread which suggests a reset - I would like to know if this is the final solution to fix this issue?

2. I can't manage to get over the IpcNotify_syncAll(SystemP_WAIT_FOREVER); line.

All I get in the console is:

[IPC Spinlock Sharedmem] Example started ...

Waiting for all cores to start ...

This project in theory is loaded into all cores and the first two has the spinlock defined.

If debug is started on all cores (prev screenshot) this IpcNofity_syncAll should not be passed?

What do I miss?

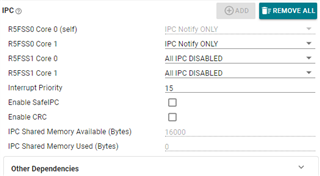

The IPC setting was not changed and looks like this:

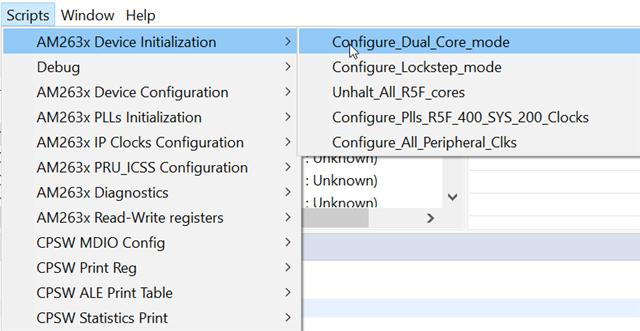

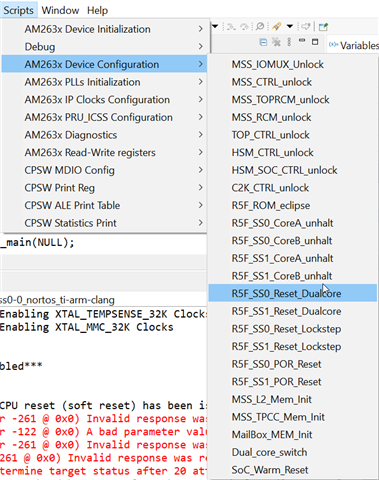

What I am not sure about are the gel files - by default only core0 has it set, it is empty for the rest.

Should this be set for all of them? Tried just in case, no change :)

I have seen suggestions on other threads to remake project from scratch to make it work but I did not succeed.

Just for the sake of testing I tried two more projects:

- ipc_notify_echo_am263x-cc_r5fss0-0_freertos_ti-arm-clang: locks into ipc_notify_echo_main_core_start/IpcNotify_syncAll(SystemP_WAIT_FOREVER);

Did restarted the devboard on all occasionsto reset all cores.

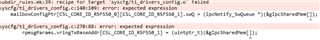

- ipc_safeipc_echo_am263x-lp_r5fss0-0_freertos_ti-arm-clang but that one has some errors:

Best regards