Other Parts Discussed in Thread: HALCOGEN

Tool/software:

Dear All,

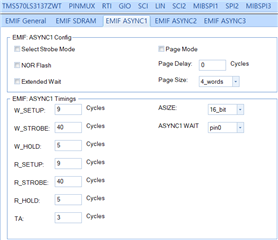

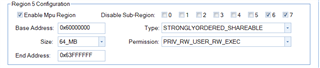

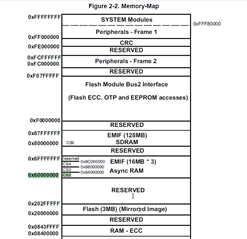

We are conducting an EMIF communication test by connecting TMS570LS3137 and FPGA.

This is a test that writes data from the FPGA when you try to read the address of the EMIF area in TMS570.

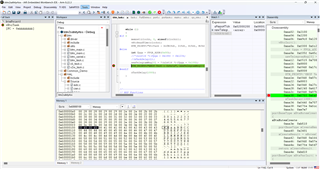

First, I briefly performed an EMIF Read/Write test on TMS570 as follows.

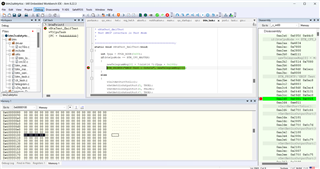

int fpga = FPGA_ADDR(0x00);

*(uint16 *)(fpga + 0x100) = 0x1234;

newTelegramMsg[0] = *(uint16 *)(fpga + 0x100);

The newTelegramMsg[0] value was read normally at 0x1234.

However, the EMIF test between TMS570 and FPGA did not work well.

In TMS570

newTelegramMsg[0] = *(uint16 *)(fpga + 0x100);

If you do something like the code above

The FPGA recognizes the CS and OE pins and loads data on the data line. When you read the data sent from the FPGA, values like 0x40, 0x41... are read.

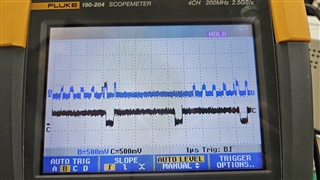

Is this a timing issue?

So what should we do?

Best Regards,

IBLEE