Tool/software:

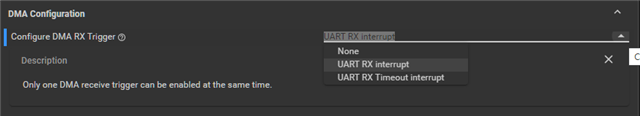

1、 DMA can only support one interrupt, how should timeout reception be implemented?

2、I want to transmit 16 mechanism data, and the bus is idle for a period of time to consider the reception complete. Can this timeout mechanism be configured on the hardware? How should it be configured specifically?

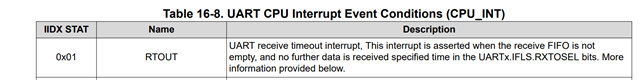

3、How is the DL_UART_DMA_INTERRUPT_RX_TIMEOUT triggered?