Tool/software:

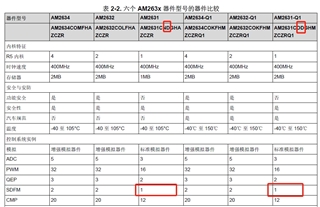

environment: CCS12.7 sdk9.0.02 I used my own PCB with 263x

configured SDFM0 in syscfg: use filter channel 4, IO set SDFM CLK Pin A15 Data Pin C14

configured SDFM1 in syscfg: use filter channel 3/4, IO set SDFM CLK Pin B13&A13 Data Pin B12&A12

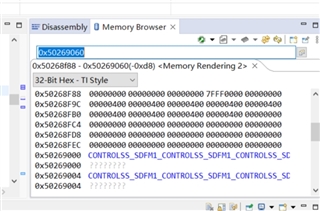

complier and run, code goes to bellow, I even didn't configure about interrupt

void __attribute__((interrupt("ABORT"), section(".text.hwi"),weak)) HwiP_data_abort_handler_c(void)

{

volatile uint32_t loop = 1;

while(loop!=0U)

{

;

}

}

My code is bellow:

void init_sigmaDelta(void)

{

/* Over value threshold settings */

uint16_t hlt = 0x7FFF;

/* Under value threshold settings */

uint16_t llt = 0x0000;

/* Configure Modulator Clock rate = Modulator data rate */

SDFM_setupModulatorClock(SDFM_VBUS_BASE_ADDR, SDFM_FILTER_4, SDFM_MODULATOR_CLK_EQUAL_DATA_RATE); //VBUS

SDFM_setupModulatorClock(SDFM_UW_PHASE_BASE_ADDR, SDFM_FILTER_3, SDFM_MODULATOR_CLK_EQUAL_DATA_RATE);

SDFM_setupModulatorClock(SDFM_UW_PHASE_BASE_ADDR, SDFM_FILTER_4, SDFM_MODULATOR_CLK_EQUAL_DATA_RATE);

SDFM_enableSynchronizer(SDFM_VBUS_BASE_ADDR, SDFM_FILTER_4, SDFM_CLOCK_SYNCHRONIZER | SDFM_DATA_SYNCHRONIZER);

SDFM_selectClockSource(SDFM_VBUS_BASE_ADDR, SDFM_FILTER_4, SDFM_CLK_SOURCE_CHANNEL_CLK);

SDFM_configEnhancedComparator(SDFM_VBUS_BASE_ADDR, (SDFM_FILTER_4 | SDFM_FILTER_SINC_3 | SDFM_SET_OSR(32)), SDFM_THRESHOLD(32767,0), \

SDFM_THRESHOLD(32767,0), (SDFM_HTLZ_DISABLE | 32767));

SDFM_selectCompEventSource(SDFM_VBUS_BASE_ADDR, SDFM_FILTER_4 , SDFM_COMP_EVENT_1 , SDFM_COMP_EVENT_SRC_COMPH1);

SDFM_selectCompEventSource(SDFM_VBUS_BASE_ADDR, SDFM_FILTER_4 , SDFM_COMP_EVENT_2 , SDFM_COMP_EVENT_SRC_COMPL1);

SDFM_configDataFilter(SDFM_VBUS_BASE_ADDR, (SDFM_FILTER_4 | SDFM_FILTER_SINC_3 | SDFM_SET_OSR(128)), \

(SDFM_FILTER_ENABLE | SDFM_DATA_FORMAT_16_BIT | SDFM_SHIFT_VALUE(7)));

SDFM_enableMainFilter(SDFM_VBUS_BASE_ADDR);

SDFM_enableSynchronizer(SDFM_UW_PHASE_BASE_ADDR, SDFM_FILTER_3, SDFM_CLOCK_SYNCHRONIZER | SDFM_DATA_SYNCHRONIZER);

SDFM_enableSynchronizer(SDFM_UW_PHASE_BASE_ADDR, SDFM_FILTER_4, SDFM_CLOCK_SYNCHRONIZER | SDFM_DATA_SYNCHRONIZER);

SDFM_selectClockSource(SDFM_UW_PHASE_BASE_ADDR, SDFM_FILTER_3, SDFM_CLK_SOURCE_CHANNEL_CLK);

SDFM_selectClockSource(SDFM_UW_PHASE_BASE_ADDR, SDFM_FILTER_4, SDFM_CLK_SOURCE_CHANNEL_CLK);

SDFM_configEnhancedComparator(SDFM_UW_PHASE_BASE_ADDR, (SDFM_FILTER_3 | SDFM_FILTER_SINC_3 | SDFM_SET_OSR(32)), SDFM_THRESHOLD(32767,0), \

SDFM_THRESHOLD(32767,0), (SDFM_HTLZ_DISABLE | 32767));

SDFM_selectCompEventSource(SDFM_UW_PHASE_BASE_ADDR, SDFM_FILTER_3 , SDFM_COMP_EVENT_1 , SDFM_COMP_EVENT_SRC_COMPH1);

SDFM_selectCompEventSource(SDFM_UW_PHASE_BASE_ADDR, SDFM_FILTER_3 , SDFM_COMP_EVENT_2 , SDFM_COMP_EVENT_SRC_COMPL1);

SDFM_configEnhancedComparator(SDFM_UW_PHASE_BASE_ADDR, (SDFM_FILTER_4 | SDFM_FILTER_SINC_3 | SDFM_SET_OSR(32)), SDFM_THRESHOLD(32767,0), \

SDFM_THRESHOLD(32767,0), (SDFM_HTLZ_DISABLE | 32767));

SDFM_selectCompEventSource(SDFM_UW_PHASE_BASE_ADDR, SDFM_FILTER_4 , SDFM_COMP_EVENT_1 , SDFM_COMP_EVENT_SRC_COMPH1);

SDFM_selectCompEventSource(SDFM_UW_PHASE_BASE_ADDR, SDFM_FILTER_4 , SDFM_COMP_EVENT_2 , SDFM_COMP_EVENT_SRC_COMPL1);

SDFM_configDataFilter(SDFM_UW_PHASE_BASE_ADDR, (SDFM_FILTER_3 | SDFM_FILTER_SINC_3 | SDFM_SET_OSR(128)), \

(SDFM_FILTER_ENABLE | SDFM_DATA_FORMAT_16_BIT | SDFM_SHIFT_VALUE(7)));

SDFM_configDataFilter(SDFM_UW_PHASE_BASE_ADDR, (SDFM_FILTER_4 | SDFM_FILTER_SINC_3 | SDFM_SET_OSR(128)), \

(SDFM_FILTER_ENABLE | SDFM_DATA_FORMAT_16_BIT | SDFM_SHIFT_VALUE(7)));

SDFM_enableMainFilter(SDFM_UW_PHASE_BASE_ADDR);

}

and mainloop:

int main(void)

{

System_init();

Board_init();

init_sigmaDelta();

while(1);

Board_deinit();

System_deinit();

return 0;

}

When I delete sdfm0 or sdfm1, the code runs properly, I tried many times, no matter how the channels are matched, as long as 2 SDFMs are configured at the same time, errors will occur.

When I run code on evaluation board, everything goes fine include 2 SDFMs work together, but on my own board, the 2 SDFMs cannot configure together, why? I ran other peripherals like spi/pwm/uart/adc/dac……everything goes fine except 2 SDFMs configure together