Part Number: AM2432

Other Parts Discussed in Thread: SYSCONFIG,

Tool/software:

Hello TI support,

from the Motor Control SDK 09.02, I'm using the SDFM example with phase compensation which we need to get reliable data.

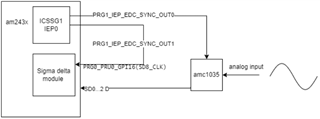

In the TI example, the clock (SYNC_OUT1) returning as "clock in" (SD8_CLK) has to be rooted externally, with a physical wire.

Is it possible to do this connection internally, without having to root any external wire? From the TRM I understand that the SDFM only accepts external signals. In our PCB design, we have a conflict of GPIO if we must use external signal.

Thank you, regards, Gael Messager