Other Parts Discussed in Thread: SYSCONFIG

Tool/software:

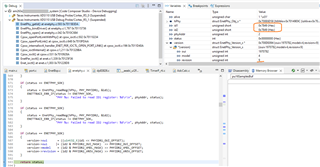

I am trying to use CPSW on a custom PCB. My SysConfig project is configured to use Port 2. The PHY is bootstrapped for ADDR == 2. I implemented a BSP to facilitate binding the driver to this port. However, I see what appears to be MDIO read errors. In EnetPhy_getId(), values read from PHY_PHYIDR1, and PHY_PHYIDR2 seen here:

… do not match the expected values in the datasheet, seen here:

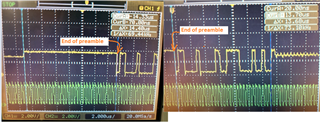

Upon probing the MDIO bus with an oscilloscope, I see that the MDIO bus has what looks like reasonable signal integrity, but the bus is very ‘chatty’. Every ~80us I see what looks like a repeated-identical transaction. This persists when the processor is halted at a breakpoint. Also, without parsing the transaction, it looks reasonably like it conforms to the frame format defined in:

AM263Px Sitara Microcontrollers Technical Reference Manual (spruj55), Section:3.2.1.4.9.1 MDIO Frame Formats,

One transaction is captured in these two images:

As mentioned above, there will be another identical transaction in less than 80us.

Reading spruj55, section 13.2.1.4.9.2 MDIO Functional Description, seen here:

… prompted me to attempt to read the CPSW_MDIO_USER_ACCESS_REG_k GO.

Rationale: Hardware must be initiating the transactions I see on the oscilloscope.

Reading:

AM263Px Sitara Microcontrollers Register Addendum (spruj57)

seen here:

… and here:

… prompted me to use the following Watch Expressions:

*((uint32_t *) 0x52820F80)

*((uint32_t *) 0x52820F80)

However, the register values I read are not consistent with the behavior. I read zero for both CPSW_MDIO_USER_ACCESS_REG_k as seen here:

I expected the GO bit to be set in at least one of the two registers.

1)

Are my watch expressions correct?

2)

Are my assumptions about the ‘chatty MDIO’ behavior and its relationship to CPSW_MDIO_USER_ACCESS_REG_k GO bit correct?