Other Parts Discussed in Thread: SYSCONFIG

Tool/software:

Hi,

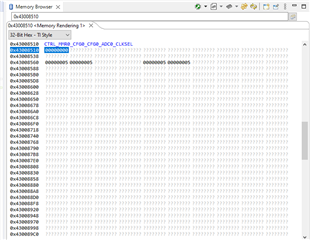

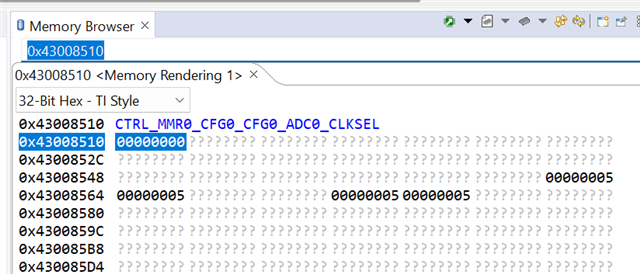

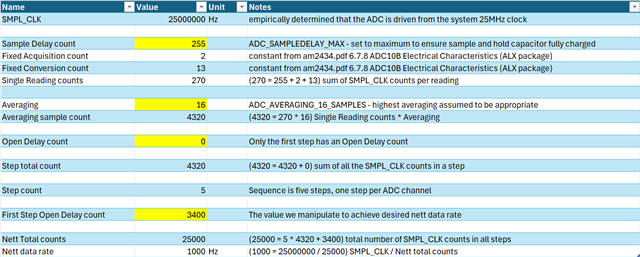

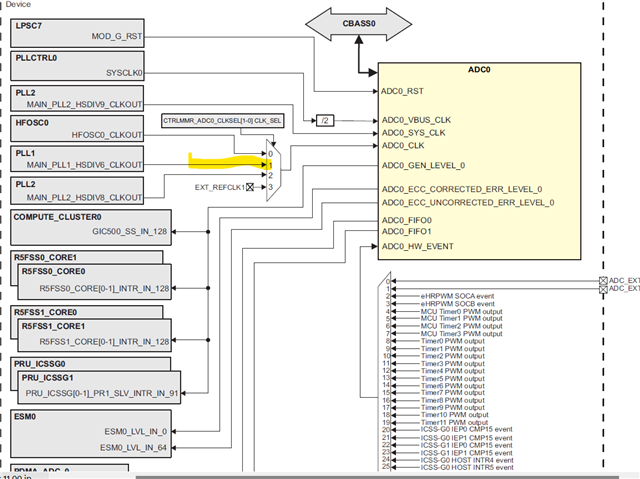

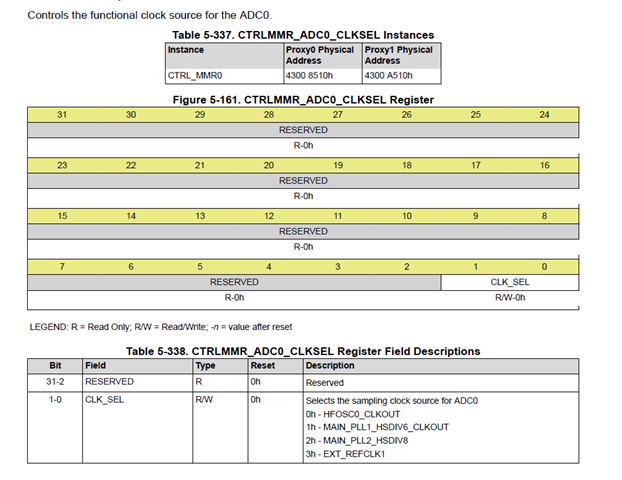

As per title, I discovered, through empirical measurements, that my AM2434's ADC has a SMPL_CLK of 25MHz. This contradicts the documentation (data sheet) which mentions 60MHz.

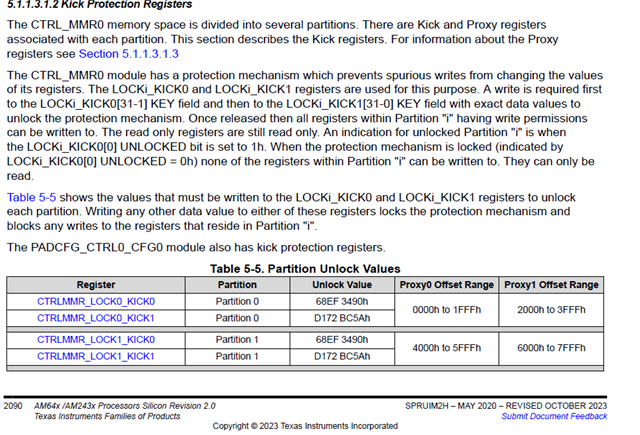

How can I set the SMPL_CLK to 60MHz? I presume setting-up an on-chip PLL. The documentation in the SDK for this, and the ADC is a bit sparse - any help appreciated.

Thanks, Steve